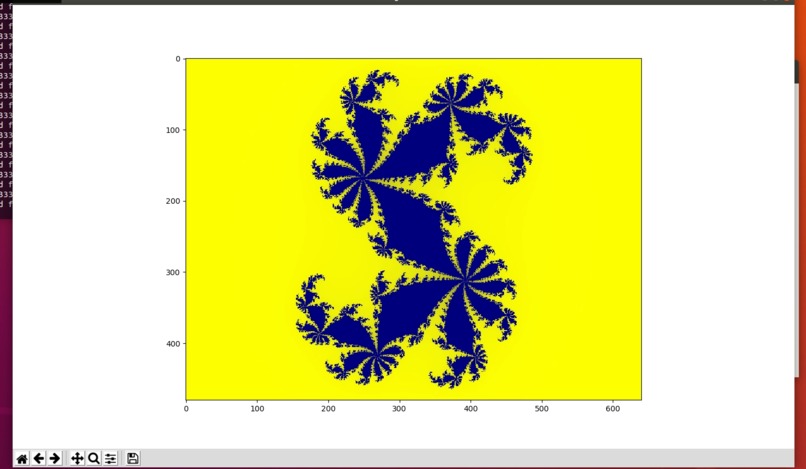

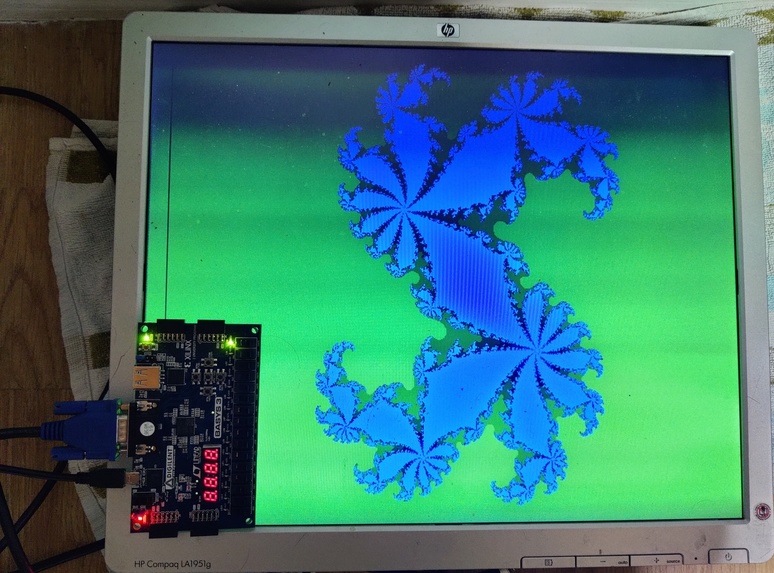

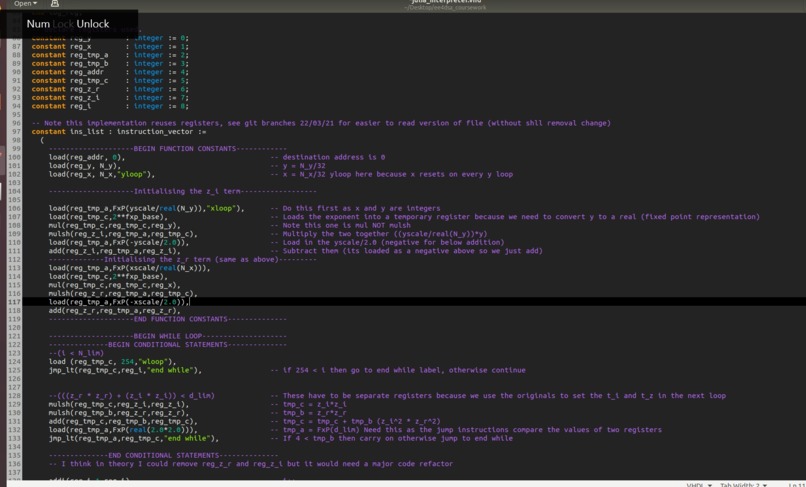

This is a VHDL Implementation of a 32-bit RISC Architecture to form a Microprocessor that generates a VGA output based on a mathematical calculation performed in assembly code.

Each pixel colour represents the number of iterations the assembly code performs before reaching a limit condition. This fractal set is called a Julia set.

This simple mathematical formula is supposed to demonstrate how different components of a CPU interact with each other such as the ALU, ROM and Dual Port Ram. Considerations have to be kept in mind when allocating memory for registers and performing calculations using fixed-point representations.

Built With

- assembly-code

- fpga

- vhdl

Log in or sign up for Devpost to join the conversation.