# HIPEAC info

# 72

JUNE 2024

ACACES

2024

Fiuggi

**EU policy directions, from artificial intelligence to cyber resilience**

**Adventures in cybersecurity, from hardware to systems**

**Lessons in launching a cybersecurity assessment business**

4

## Recent EU policy developments

## Cybersecurity, the NCP and the HiPEAC Vision

22

## Digital guardians: HiPEAC vs. cyberattacks

|    |                                                                                                                                                                                                                                                                                                                            |    |                                                                                                                                                                                                                                                                                                                                                                           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3  | Welcome<br><i>Koen De Bosschere</i>                                                                                                                                                                                                                                                                                        | 36 | SME snapshot<br><b>Software development for real-time critical systems with TASKING</b><br><i>Alexander Herz</i>                                                                                                                                                                                                                                                          |

| 4  | Policy corner<br><b>Powering the digital and green transitions: Recent EU policy developments</b><br><i>Jan Komarek</i>                                                                                                                                                                                                    | 37 | Innovation Europe<br><b>Handling health data with confidence: How SECURED enables secure processing, anonymization and synthetic generation</b><br><i>Francesco Regazzoni, Paolo Palmieri and Apostolos Fournaris</i>                                                                                                                                                     |

| 6  | News                                                                                                                                                                                                                                                                                                                       | 38 | Innovation Europe<br><b>SAFE4SOC: Defining a cyber and physical incident-detection format to facilitate cybersecurity collaboration</b><br><i>Gilles Lehmann</i>                                                                                                                                                                                                          |

| 18 | Cybersecurity special<br><b>Threats on the horizon: Cybersecurity, the 'next computing paradigm' and the HiPEAC Vision</b><br><i>Olivier Zendra</i>                                                                                                                                                                        | 39 | Innovation Europe<br><b>EOSC-ENTRUST: Driving European interoperability for sensitive-data access and analysis</b><br><i>Elaine Harrison</i>                                                                                                                                                                                                                              |

| 20 | Cybersecurity special<br><b>Lighting the way to better security: The NEUROPULS photonics-based approach</b><br><i>Fabio Pavanello</i>                                                                                                                                                                                      | 40 | Innovation Europe<br><b>eFlows4HPC delivers a European HPC workflow platform</b><br><i>Renata Giménez</i>                                                                                                                                                                                                                                                                 |

| 22 | Cybersecurity special<br><b>Digital guardians: How HiPEAC takes on cyberattacks</b><br><i>Vasilis Mavrikakis, David Andreu, Martí Alonso, Beatriz Otero, Juan José Costa, Enric Morancho, Stefano Di Carlo, Cristiano Pegeraro Chenet, Alessandro Savino, Ramon Canal, Lars Creutz, Guido Dartmann, Alessandro Palumbo</i> | 41 | Innovation Europe<br><b>Introducing EMPYREAN's hyper-distributed paradigm for the IoT-edge-cloud continuum</b><br><i>Anastassios Nanos, Panagiotis Kokkinos and Emmanouel (Manos) Varvarigos</i>                                                                                                                                                                          |

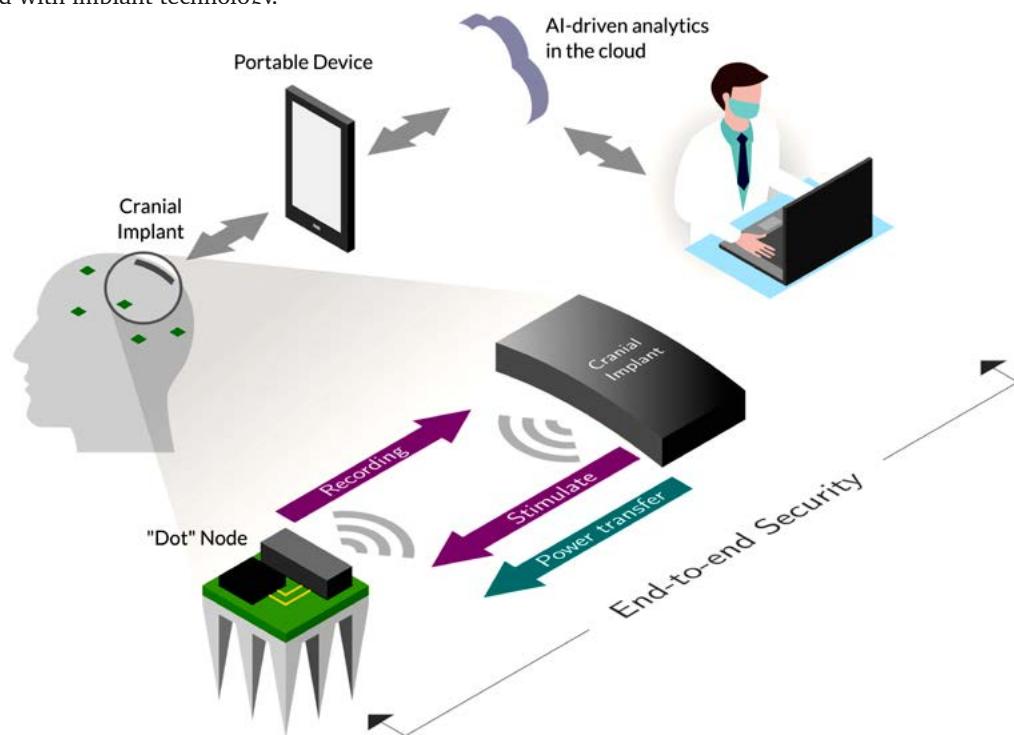

| 28 | Cybersecurity special<br><b>Brain gain or brain drain? The risky rise of connected neural implants</b><br><i>Christos Strydis and Muhammad Ali Siddiqi</i>                                                                                                                                                                 | 42 | Innovation Europe<br><b>Flying high: FALCON's quest for quieter, smarter air transport</b><br><i>Anaïs Lourdières</i>                                                                                                                                                                                                                                                     |

| 30 | Cybersecurity special<br><b>Resilience from day 1: An overview of research working towards secure-by-design systems</b><br><i>Francesco Regazzoni and Paolo Palmieri</i>                                                                                                                                                   | 43 | Innovation Europe<br><b>Ensuring the supply of antivirals for pandemic response with AVITHRAPID</b><br><i>Silvano Coletti</i>                                                                                                                                                                                                                                             |

| 31 | Innovation impact<br><b>ORBIK Cybersecurity</b><br><i>Salvador Trujillo</i>                                                                                                                                                                                                                                                | 44 | Industry focus<br><b>'Cloudian makes it easy to expand the data lake'</b><br><i>Sascha Ühl and Stuart Cording</i>                                                                                                                                                                                                                                                         |

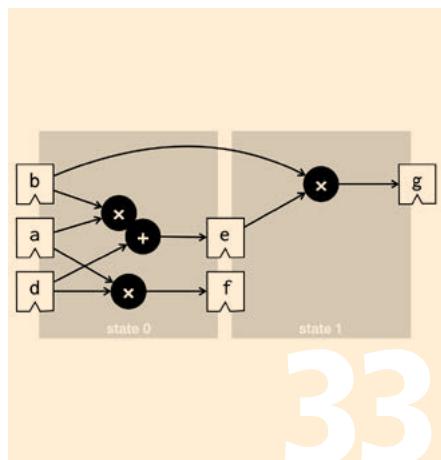

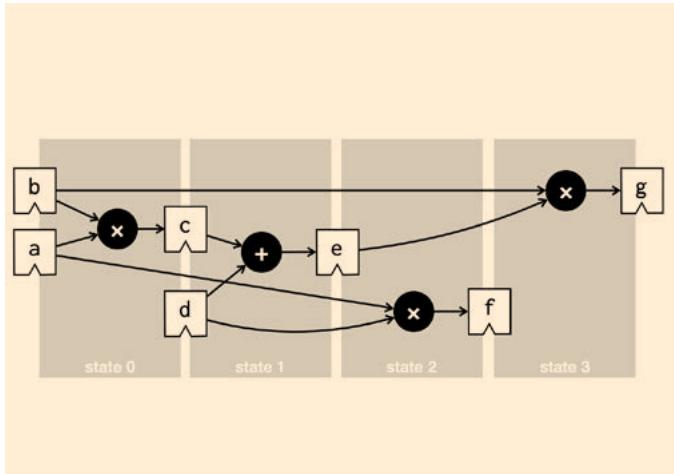

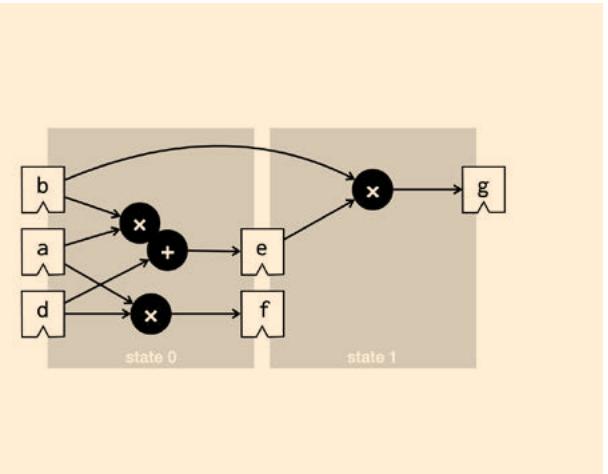

| 32 | Peac performance<br><b>Faster hardware with verified high-level synthesis</b><br><i>Yann Herklotz and John Wickerson</i>                                                                                                                                                                                                   | 44 | HiPEAC futures<br><b>Career talk: Virginia Niculescu</b><br><b>'WHPC provides a "safe space" where people can share experiences'</b> – Sara Royuela<br><b>'HiPEAC's most valuable asset lies in shaping the next generation of specialists'</b> – Laura Menéndez<br><b>Three-minute thesis: Field programmable gate array (FPGA) acceleration of healthcare analytics</b> |

| 34 | Technology opinion<br><b>Secure-by-design systems need memory safety and design provenance</b><br><i>Ron Black</i>                                                                                                                                                                                                         |    |                                                                                                                                                                                                                                                                                                                                                                           |

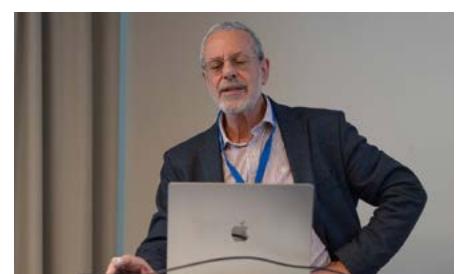

## How to launch a cybersecurity assessment company

Spanning the compute continuum from edge to cloud, HiPEAC (High Performance, Edge And Cloud computing) is a network of over 2,000 world-class computing systems researchers, industry representatives and students. First established in 2004, the project is now in its seventh edition. HiPEAC7 focuses on networking and roadmapping activities: bringing the computing community together in Europe, exchanging ideas, building thriving European value chains and exploring the long-term vision for computing systems.

[hipeac.net](http://hipeac.net) [@hipeac / @hipeacjobs](https://twitter.com/hipeac)

[hipeac.net/linkedin](http://hipeac.net/linkedin) [YouTube](https://www.youtube.com/hipeac) [hipeac.net/tv](http://hipeac.net/tv)

**Funded by

the European Union**

The HiPEAC project has received funding from the European Union's Horizon Europe research and innovation funding programme under grant agreement number 101069836. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

**Cover image:** Andrii Yalanskyi / Adobe Stock

**Design:** [www.magelaan.be](http://www.magelaan.be)

**Editor:** Madeleine Gray

## Faster hardware with verified high-level synthesis

## Career talk: Virginia Niculescu, Babeş-Bolyai University

The theme of this magazine is cybersecurity. HiPEAC has covered cybersecurity in computing since the first HiPEAC Vision document in 2007, but it is fair to say that most computer architects are more concerned about performance and power consumption than about cybersecurity. In the last decade, there have been several cases in which performance-enhancing optimizations have been exploited to set up attacks, like Spectre and Meltdown.

Unfortunately, security is of growing importance, and we are currently in a perfect storm. No modern society or large company can function properly without digital technology to support its basic functions: communications, financial transactions, mobility, energy, .... Attacking a few servers is sometimes enough to disrupt an organization – in some cases for weeks.

Modern systems based on the IoT-edge-cloud computing continuum are even more vulnerable to attacks because they expose a larger attack surface. A server in a datacentre is easier to protect (both physically and logically) than a network of sensor nodes and edge computers in a power grid, for example. The recent trend of edge artificial intelligence (AI), combined with local control for actuation, can further increase the impact of an attack because it can also compromise safety.

Finally, there is cyber warfare. Cyberspace is now generally recognized as the fifth domain of warfare, after land, sea, air and space. All major countries have created cyber armies to defend critical infrastructure, and to build capability to attack other countries. Attacks range from disrupting the critical infrastructure of a country (power grid, public transportation, emergency services, water supply), to destabilizing society with fake news. The current tensions between the European Union (EU) and Russia, China and the Middle East have increased the intensity of such attacks. Elections and big international events like the Olympic games are another opportunity to interfere in the public debate.

All the above has been going on for years, but it has accelerated with the advent of powerful AI-based tools. The tools cannot only be used to set up or defend against attacks, but also to influence public opinion, and to create unrest.

In conclusion, I believe that our community has not only the responsibility but also the moral obligation to make our systems secure by design. Cybersecurity is too important to be an afterthought, and we should put more effort in it (both in hardware and in software). I hope that this magazine will give you some inspiration.

Koen De Bosschere, HiPEAC coordinator

From the AI Act to the Cyber Resilience Act: in this article, Jan Komarek, policy offer in the European Commission's Internet of Things Unit and HiPEAC project officer, sets out recent policy developments and their implications for the computing systems community.

## Powering the digital and green transitions: Recent EU policy developments

Together with the strategic research agendas of European industrial associations, the HiPEAC Vision is a key strategic document for the European Commission when defining its research and innovation programmes. In parallel with technology advancements, in recent years the Vision has also referred to the geopolitical situation surrounding Europe, which has increased competition and tensions. We are witnessing technology races between the United States and China, and Europe has to find its position. This has been articulated in the 'races' outlined in the HiPEAC Vision 2024 – namely, for the 'next computing paradigm', for artificial intelligence, for new hardware technologies, for cybersecurity, and for sustainability, with the sovereignty of Europe a key issue in each area.

These races also resonate with the European strategy for achieving digital sovereignty and competitiveness, which aims to provide the framework for digital innovation in Europe. Below are some of the main policy developments in recent months.

In December, the European Parliament and the Council of the European Union (EU) reached a political agreement on the **Artificial Intelligence Act**, the first legislation of its kind in the world. The AI Act intends to prohibit biometric identification, untargeted scraping of

facial images from the internet or CCTV footage, emotion recognition or social scoring. Artificial intelligence systems that exploit the vulnerabilities of people or manipulate human behaviour to circumvent their free will are to be curbed by this legislation as well. Deployers of high-risk AI systems will have to conduct a fundamental rights impact assessment prior to putting an AI system into use.

Of course, the regulation is set up so that we keep the innovation space open. European negotiators also agreed on a series of safeguards for the use of biometric identification systems in publicly accessible spaces for law enforcement purposes under strictly defined conditions. The AI Act comes at a time when AI applications are being rolled out in many different scenarios,

resulting in even more requirements for computing systems. For example, the AI inference phase in autonomous driving requires special-purpose processors that are both inexpensive and provide results in real time.

The conviction that we are stronger when we join forces at EU level is at the heart of our vision for Europe's digital transformation to be achieved by 2030. This is expressed in the **Digital Decade** policy programme. It is driving our implementation strategy in digital through its ambitious 2030 targets, which are structured around four key pillars: investing in digital infrastructures, the digital transformation of business, the digital transformation of the public sector, and, of course, digital skills. In particular, it aims to double EU share

in global production of cutting-edge semiconductors and provide for 10,000 climate-neutral highly secure edge nodes.

With the European strategy for data adopted in 2020, we are making Europe a leader in the data economy by creating a genuine single market for data. With computing power moving closer to where the data is, data legislation has a strong influence on the rules across the computing continuum. The European Commission is putting forward the legislative framework for a prospering data economy. For example, the **Data Act**, which came into force in January 2024, will make more data available for use, in particular industrial data. It will set up rules on who can use and access what data for which purpose. Furthermore, with its cloud strategy, Europe is deploying secure, interoperable, and low-carbon cloud and edge services and infrastructures across Europe.

Hardware is not forgotten, either: the European **Chips Act**, which came into force on 2023, will help reinforce the European semiconductor ecosystem, increase the security and resilience of our supply chains, and strengthen our technological sovereignty. This will help achieve both the digital and green transition. The Chips Joint Undertaking is supporting these advancements and it has already launched its first call in November with €1.7 billion of EU funding. The Chips Act is one of several initiatives announced by the Commission over the last three years that address Europe's technical sovereignty, following the initiative on batteries, and being followed this year by the initiative on reducing dependencies on third countries for critical raw materials.

Europe's sovereignty has also been supported by the European **High Performance Computing Joint Undertaking**, which has procured nine super-

The Leonardo supercomputer is among the best in the world. Credit: CINECA

computers, located across Europe. At the time of writing, two of them – Italy's Leonardo and Spain's MareNostrum – are in the top 10 of the Top500 list of supercomputers worldwide. Meanwhile, efforts to extend the secure and hyper-connected supercomputing, quantum computing, service- and data-infrastructure ecosystem will continue.

Finally, the **Cyber Resilience Act** approved by the European Parliament in March 2024 is of particular relevance to this issue of *HiPEACinfo*. This aims to address the twin problems of inadequate levels of security in many products, and the inability of consumers and businesses to currently determine which products are cybersecurity, or to set them up in a way that ensures their cybersecurity is protected. To do so, the Cyber Resilience Act lays down a uniform legal framework for essential cybersecurity requirements for bringing products with digital elements to the EU market, covering the planning, design, development and maintenance of such products.

In addition to these legislative advances, the European Commission has also

been allocating funding for computing systems research. To give a few examples, recent calls in the Horizon Europe Work Programme have sought project proposals on next-generation edge computing technologies and open-source for cloud and edge computing, while last year's funding programme included calls for research projects relating to intelligent data processing. With the DISCOVER-US project launched in January 2024, the Commission also aims to further research into swarm intelligence and distributed computing in collaboration with the National Science Foundation in the United States.

Given the HiPEAC Vision's role as a major reference for the formulation of research and innovation programmes, it is likely that this will apply to the context of the next work programme for Horizon Europe, for the year 2025 and beyond. We look forward to proposals from this community which will help Europe deliver the digital and green transitions with secure computing systems, responsible AI, a prospering and privacy-respecting data economy, and designed-in-Europe computing infrastructure.

# Record attendance at HiPEAC 2024 in Munich

With almost 700 registered participants from 36 countries, the 2024 HiPEAC conference had the highest attendance of any event organized by HiPEAC in its 20-year history. Taking place in Munich on 17-19 January 2024, the conference was once again an excellent opportunity to catch up with colleagues and find out about the latest computing systems research.

'We are very proud to have hosted the largest HiPEAC conference to date, with close to 700 participants this year, as well as raising the highest amount of sponsorship so far,' said Diana Görninger (TU Dresden), general chair of HiPEAC 2024. 'The programme was also huge, covering everything from edge through cloud to high-performance computing.'

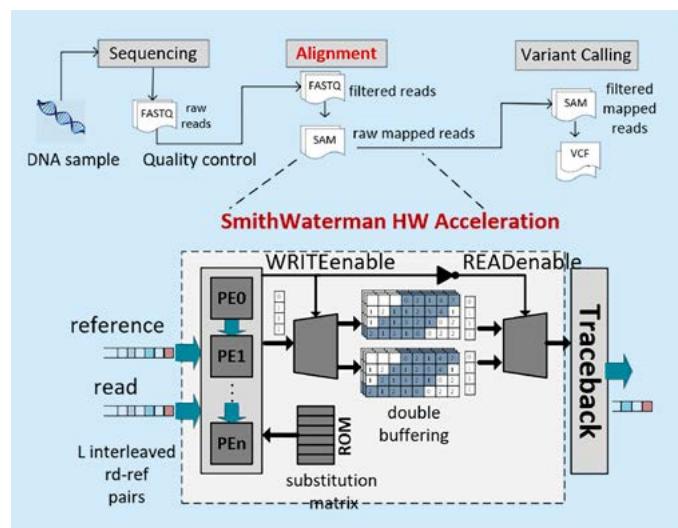

The conference keynote talks covered three compelling topics. Reetuparna Das (University of Michigan) set out how the demands of genomics applications are challenging systems to new levels of performance. Lieven Eeckhout (Ghent University) made a cogent case for the importance of sustainability in computing systems research, while Mitsuhsisa Sato (RIKEN) discussed the design of the mighty Fugaku supercomputer and offered a glimpse into post-exascale computing. Meanwhile, Jan Komarek of the European Commission also updated the community on the latest policy developments, as set out in the 'Policy corner' article in this issue of *HiPEACinfo* (pp. 4-5).

The paper track featured presentations of articles published in ACM TACO, thanks to HiPEAC's journal-first model, covering topics including runtime optimization, machine learning, and emerging devices. With 32 workshops and 11 tutorials, there were also a plethora of parallel events to choose from, exploring the latest advances in edge artificial intelligence (AI), the computing continuum, next-generation communications, neuromorphic and quantum computing, high-performance computing, and much more. Participants also had the opportunity to visit the nearby Lebiniz Supercomputing Centre.

The 2024 edition was testament to the ever-increasing role played by industry in the HiPEAC conference: having once again broken sponsorship levels, the conference included a vibrant exhibition of technology companies, from spinoffs to multinationals, while the industry session was an ideal opportunity for networking. Careers development and student-industry interaction were also key features of the conference, with activities including the HiPEAC Student Challenge and an Inspiring Futures careers session featuring representatives from companies.

The conference wouldn't have been complete without its social event, which this year took place in the convivial setting of Munich's famous Hofbräuhaus. During the dinner, a ceremony was held to celebrate the winners of the 2023 HiPEAC Technology Transfer Awards, who were congratulated in front of the 500-strong audience.

It goes without saying that the success of this year's conference was in large part due to the generosity of the 31 sponsors who supported the event, and to the commitment of the organizing team. For 2024, the general chair was Diana Görninger, the programme chair was Hayden So (University of Hong Kong), and the local chair was Stefan Wallentowitz (Hochschule München University of Applied Sciences). Longstanding committee members include Sascha Uhrig (workshops chair), Daniel Gracia (industry chair), and Dezun Dong, Diego R. Llanos and Gaspar Mora Porta (all publicity chairs).

↗ [hipeac.net/2024/munich](http://hipeac.net/2024/munich)

HiPEAC24 Google Photos album

↗ [bit.ly/HiPEAC24\\_photos](http://bit.ly/HiPEAC24_photos)

HiPEAC24 on HiPEAC TV – including full keynote talks

↗ [bit.ly/HiPEAC24\\_videos](http://bit.ly/HiPEAC24_videos)

# Have your say on the HiPEAC Vision 2025

The HiPEAC Vision editorial board is currently preparing the 2025 HiPEAC Vision, setting out the computing challenges that private and public investments should address to get Europe ahead in the technology race.

The HiPEAC Vision 2025 will be centred on the 'next computing paradigm' (NCP). More details on this can be found in the following paragraphs and in the HiPEAC Vision 2024 (see 'Further reading', below).

The NCP envisions the convergence of the web, cyber-physical systems (CPS), the cloud, the internet of things (IoT) and digital twins into a coherent, federated, dynamic and intelligent continuum of computing.

The resources needed to execute service requests in the NCP will be dynamically orchestrated by edge-based generative artificial intelligence (AI) in a manner that balances availability, privacy, provenance, latency, energy, decentralization, personalization and context awareness, delivering users from the all-absorbing pull of the cloud.

The NCP will be a 4D computing paradigm that elevates the 2D plane of the current web into a time-sensitive spatial (spatial hence 3D, plus time for 4D) web-based space that intertwines the physical and the digital worlds in a unified networked infrastructure where services and data move fluidly, opportunely, seamlessly and interoperably.

The HiPEAC Vision editorial board is seeking feedback from the community on this vision. Have you heard of the NCP – and if so, was it from HiPEAC or from elsewhere? Do you agree with this vision of the evolution of computing? Do you agree that it is attractive for next-generation applications, and / or strategically important for business and the economy? What are the main technical challenges involved in achieving this vision?

You can have your say by responding to this brief survey:

[hipeac.typeform.com/to/bSd4xm](https://hipeac.typeform.com/to/bSd4xm)

## FURTHER READING:

HiPEAC Vision 2024 [hipeac.net/vision/2024.pdf](https://hipeac.net/vision/2024.pdf)

T. Vardanega and M. Duranton. 'HiPEAC's Vision for the Future: Envisioning the next computing paradigm' on the Communications of the ACM blog, 1 May 2024

[cacm.acm.org/blogcacm/hipeacs-vision-for-the-future](https://cacm.acm.org/blogcacm/hipeacs-vision-for-the-future)

Vardanega, T., & Duranton, M. (2024). 'The Next Computing Paradigm: an Introduction' in the HiPEAC Vision 2024, Rationale

[doi.org/10.5281/zenodo.10874349](https://doi.org/10.5281/zenodo.10874349)

## Key cybersecurity concerns for European MetaOS projects

On 10 April 2024, the 'Meta Operating Systems (MetaOS) Workshop', organized by Jan Komarek and Rolf Riemenschneider (European Commission), took place in Brussels. The workshop brought together project representatives, experts and stakeholders to discuss ongoing work in the EUCloudEdgeIoT initiative and set out future directions for the computing continuum.

Following presentations covering the work of the six task forces under the EUCloudEdgeIoT umbrella in the morning, the afternoon session explored cross-cutting topics including platform integration, standardization, and cybersecurity.

The cybersecurity session discussed the need for cybersecurity measures at all layers from internet-of-things (IoT) devices up to central computing and storage facilities, with Jan Komarek identifying key issues for cybersecurity in MetaOS projects, particularly on the pros and cons of decentralized networks from the cybersecurity perspective.

While storing data in a single centralized location makes data protection easier and reduces the attack surface, it also presents a tempting target for attacks, as breaching the protection potentially grants access to all data. Therefore, even centralized systems often share data among multiple silos to reduce the impact of any individual breach.

The MetaOS use cases are driven by moving from centralized security management to distributed security management. The topologies add another security layer by

minimizing the transmission of sensitive data by processing at the edge and by data aggregation before transmission to the cloud. Security measures at the network edge, including firewalls, access controls, and encryption, are essential to protect data as it is transmitted to the cloud. Securing communication channels between edge devices and the cloud, for example by encryption, is critical to prevent interception.

Authentication and access control mechanisms must be enforced at the edge and on IoT devices to prevent unauthorized access to sensitive data and resources. Device identity management and role-based access control are commonly used to enforce security policies. Decisions on where to place security controls — locally on devices or centralized in the cloud — can significantly impact the system's ability to respond to and recover from attacks. Cybersecurity measures are inherent to all MetaOS networks, notably those with application in critical infrastructures as well as in healthcare sector.

What is challenging for decentralized networks is to provide for resilience ensuring that critical components continue to function with uninterrupted operation even during security attacks. Validation of the resilience of application's cybersecurity measures and response procedures is carried out by simulated real-world cyberattacks, attack scenarios such as unauthorized access attempts and data breaches. Redundancy, replication and synchronization mechanisms are necessary to ensure data resilience of distributed computing.

## DISCOVER-US webinar videos available online

DISCOVER-US is a coordination and support action that promotes networking between researchers in the European Union (EU) and United States (US), focusing on distributed computing and swarm computing. Activities include vision building, funded transatlantic research exchanges, and networking events.

The project also holds regular webinars, and several are now available to view on the HiPEAC TV YouTube channel, in a dedicated DISCOVER-US playlist.

- **DISCOVER-US EU-US Virtual Networking Event**, featuring six EU-funded projects and four projects funded by the National Science Foundation (NSF)

- **Meet DISCOVER-US**: an introduction to the DISCOVER-US project, its main aims and activities

- Rute Sofia on the **CODECO edge-cloud orchestration framework**

- Talks on different aspects of the **SmartEdge project**

- **Sage: A Software-Defined Sensor Network**, presented by Pete Beckman (formerly Argonne National Laboratory, now Northwestern University)

↗ [bit.ly/DISCOVER-US\\_webinar\\_videos](https://bit.ly/DISCOVER-US_webinar_videos)

# EuroHPC hosting entities join forces in new project to support HPC users

Paula C. Rodrigues and Rita Moutinho, INESC TEC

The EuroHPC Joint Undertaking has been working towards taking European supercomputing to new heights by installing new machines capable of competing with their global counterparts. Now, the current and future hosts of these supercomputers have combined forces to provide support services to selected users. The result is the EPICURE project (High-level specialised application support service in High-Performance Computing), featuring 16 partners from 14 different countries, and led by CSC – IT Center for Science, in Finland.

‘At the moment, most of the help provided to users is short-term support which requires basic high-performance computing (HPC) skills and competences,’ says Emmanuel Ory, development manager at CSC and coordinator of the project. ‘EPICURE will help users at an advanced technical level. Right now, all the different sites in Europe use different architectures, so users need to be able to move from one system to another very easily and seamlessly,’ continues Ory.

The project will provide several services, including code enablement and scaling, performance analysis and benchmarking, and code optimization. To this end, the project will draw on the experience and knowledge of all partners in HPC operations and support, using training activities and hackathons to share knowledge.

EPICURE’s consortium is composed by 16 organizations from 14 different countries: Barcelona Supercomputing Centre (Spain), Cineca Consorzio Unteruniversitario (Italy), IT4Innovations at VSB – Technical University of Ostrava (Czechia), Institut Informacijskih Znanosti (Slovenia), Institut Jozef Stefan (Slovenia), Luxprovide SA (Luxembourg), INESC TEC (Portugal), Sofia Tech Park JSC (Bulgaria), Universiteit Antwerpen (Belgium), Kungliga Tekniska Hoegskolan (Sweden), Akademia Gorniczo-Hutnicza IM. Stanisława Staszica W Krakowie (Poland), Danmarks Tekniske Universitet (Denmark), Forschungszentrum Julich GmbH (Germany), Grand Equipement National de Calcul Intensif (France) and Centre Informatique National de L’Enseignement Supérieur (France).

For further information, contact:  paula.c.rodrigues@inesctec.pt and  rita.moutinho@inesctec.pt

Co-funded by

the European Union

EuroHPC

Joint Undertaking

EPICURE has received funding from the European High-Performance Computing Joint Undertaking under grant agreement no. 101139786.

## EIC Pathfinder and Accelerator Challenges 2024

European

Innovation

Council

The 2024 European Innovation Council (EIC) Work Programme includes over €1.2 billion of funding for proposals focusing on breakthrough technologies and game-changing innovations which are high risk and with high potential for impact and to scale up internationally.

EIC Pathfinder challenges for this year include ‘Nanoelectronics for energy-efficient smart edge devices’. Meanwhile, EIC Accelerator challenges a number of potential interest to the HiPEAC community, including ‘Human Centric Generative AI made in Europe’, ‘Enabling virtual worlds and augmented interaction in high-impact applications to support the realisation of Industry 5.0’ and ‘Enabling the smart edge & quantum technology components’.

For further information, including the application process and deadlines, visit the EIC website.

[eic.ec.europa.eu/

eic-funding-opportunities\\_en](http://eic.ec.europa.eu/eic-funding-opportunities_en)

**“Over €1.2 billion of funding for proposals focusing on breakthrough technologies which are high risk and with high potential for impact and to scale up internationally”**

# AMBRA uses AI to help people with communication disabilities

Christian Pilato (Politecnico di Milano), Ambra Di Paola (Fondazione Artos), Serena Muraro (Fondazione Artos), and Roberto Marinelli (Fondazione Artos)

Augmentative and alternative communication (AAC) techniques leverage images and symbols to support individuals with communication disabilities. These methods help consolidate the autonomy levels of the individuals; for example, teaching them how to behave in many situations. However, individuals can understand symbols differently, meaning that personalized approaches are necessary.

A collaboration between Politecnico di Milano and Fondazione Artos, the AMBRA project is addressing these challenges by leveraging a combination of artificial intelligence (AI)-based methods to create a personalized learning environment in AAC. For example, it uses large language models to create texts or images, convolutional neural networks to automate the conversion of photos into symbols, and collaborative filtering to create personalized schedules. The AMBRA platform is cloud based and intended to be modular and easy to extend or cooperate with other AAC initiatives. For example, it leverages and extends the ARASAAC symbol library. Educators can share the learning material worldwide and further customize it to adapt to specific needs, cultures, or languages. The project is currently self-funded, leveraging support from research partners and industry to access computational resources.

Our approach aims to lower the technological, social, and cultural barriers to using AAC methods. The frontend of the AMBRA platform can run on all modern devices (such as smartphones, tablets, laptops, etc.) so that both educators and users can use it in every context, including real life.

Educators may exchange material more easily, creating a virtuous cycle that could boost the adoption of AAC methods. Having low-cost methods to create materials can encourage shops, public places, and community places to adopt such solutions and allow for a seamless transition between school and society, creating a more inclusive environment around the individuals. For example, QR codes allow users to download specific material (like a menu or a shopping list), which is later personalized based on specific user's information and symbols. This allows users to apply the autonomy concepts that have been acquired in class. AMBRA can also lower the cultural and language barriers when used with immigrants (for example using symbols from different cultures), facilitating their integration into a new community.

In conclusion, this project is intended to become a beacon to extend the use of AAC in real life. However, AMBRA's idea extends beyond its technical architecture; it embodies a vision for a more inclusive future where the boundaries of communication are pushed ever further thanks to the virtuous circle created by the combination of all these solutions, enabling society to include individuals with diverse communication needs who can express themselves with clarity and dignity in any context and without barriers. This approach can also lead to a rethink of the educator's role to be more open to worldwide collaboration in material and knowledge sharing.

Please feel free to contact us directly:

✉ [info@progetto-ambra.it](mailto:info@progetto-ambra.it)

To stay updated on project news and connect with the AMBRA team, follow the LinkedIn page:

linkedin.com/company/progetto-ambra

***"AMBRA [helps enable] society to include individuals with diverse communication needs who can express themselves with clarity and dignity in any context"***

# IT4Innovations is a new member of the iRODS Consortium

Marketa Dobiasova, IT4Innovations

IT4Innovations National Supercomputing Center (Czech Republic) has become a member of the iRODS Consortium, a group that brings together businesses, research organizations, universities and government agencies from around the world to ensure the sustainability of the iRODS software as a solution for distributed storage, transfer, and management of data.

Integrated Rule-Oriented Data System (iRODS) is open-source software that allows the storage, management and sharing of large amounts of data, including their metadata, between different organizations and platforms. It also provides a mechanism for defining rules for data storage, processing and distribution. iRODS is designed to support collaboration, interoperability and scalability of data infrastructures.

Martin Golasowski, senior researcher at IT4Innovations, summarized the benefits of membership in the iRODS Consortium: 'The demand for a comprehensive solution for fast and efficient data transfer between locations is increasing across the European scientific community. Membership of the iRODS

Consortium enables us to communicate directly with the development team and provides us with access to the latest features and support in providing tools to the scientific community and beyond.'

iRODS provides a virtual file system for various types of data storage, metadata management, and a mechanism for federating geographically distant locations for data transfer. 'These features are used in the LEXIS Platform, which simplifies the use of supercomputers to run complex computational tasks through a unified graphical interface or using a specialized application interface. The transfer of large volumes of data between supercomputers and data storage is performed automatically and transparently for those using iRODS and other data management technologies,' adds Golasowski.

The iRODS software has been deployed at thousands of locations for long-term management of petabyte data in various industries such as the oil and gas industry, biosciences, physical sciences, archives, the media and the entertainment industry.

#### FURTHER INFORMATION:

- ☞ [irods.org](http://irods.org)

- ☞ [docs.lexis.tech](http://docs.lexis.tech)

# New MAR chapter of Women in High Performance Computing

This year, a new chapter of Women in High Performance Computing (WHPC) has been opened. Named MAR-WHPC, the chapter has members from all over Spain and plans to expand to include members throughout southern Europe. The MAR chapter, which was presented by Elisabeth Ortega (HPC Now!) and Sara Royuela (Barcelona Supercomputing Center) at the HiPEAC conference in Munich, is dedicated to fostering an inclusive environment and supporting women in all stages of their high-performance computing (HPC) careers.

*Read more about MAR-WHPC in our interview with Sara Royuela on pp. 48-49.*

[linkedin.com/company/mar-whpc](https://www.linkedin.com/company/mar-whpc)

@mar\_whpc

***"MAR-HPC is dedicated to fostering an inclusive environment and supporting women at all stages of their careers"***

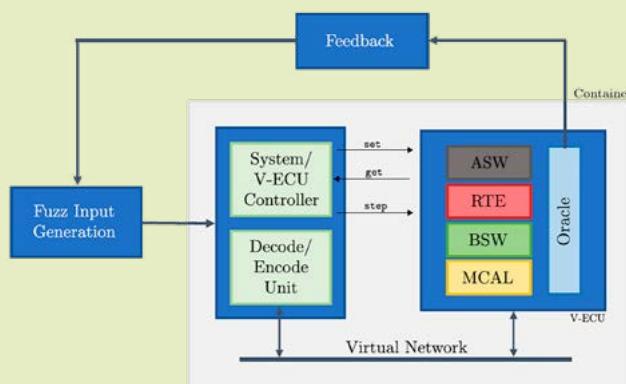

## Coverage-guided fuzzing with virtual ECUs

Martin Ring, Bosch Research

The increasing complexity of automotive software – and its subsequent impact on safety and security – means that standards have to be followed for safe and secure software development. Fuzz testing is a cybersecurity measure that generates targeted test cases to identify security vulnerabilities in software. It is recommended by ISO/SAE 21434, as well as other standards and best-practice documents, to improve not only cybersecurity but software quality in general.

To enable fuzz testing in a stateful and embedded environment such as automotive, fuzzing based on a virtual electronic control unit (V-ECU) has been explored by Bosch. This work aims at creating a paradigm shift from a black-box fuzzing approach to a grey-box source-code fuzzing approach utilizing coverage feedback.

We use the FMI (Functional Mock-up Interface) standard to build the vECU with source-code instrumentation for coverage feedback and oracle implementation. The FMI standard defines four levels of abstraction, as follows:

- single software components

- communicating software components

- fully integrated ECUs with a changed MCAL (microcontroller abstraction layer)

- target software executed with an emulator

The fuzzer generates meaningful coverage-guided mutation data, which is communicated to the V-ECU through the FMI. In addition to fuzzing the ECU via protocol interfaces such as CAN (controller area network) and Flexray, the FMI interface facilitates the fuzzing of internal variables exposed by the FMI, thus enabling grey-box fuzzing.

We focused mainly on the level three defined by the FMI standard, with a codebase up to >98% the same as the target software due to the increased speed (100x to 0.5x wall clock time (WCT)), precision and easier scalability. Using V-ECU based fuzz testing in continuous security testing (CST) increases the robustness of software developed by identifying security vulnerabilities and implementation bugs at a very early stage. The advantages shown by V-ECU fuzzing in terms of easy integration into the continuous integration / continuous deployment (CI/CD) pipeline and reduced costs are a convincing argument for the adoption of V-ECU fuzzing as a standard testing approach.

## EmLogic VHDL verification course material now available

Espen Tallaksen, EmLogic

Used by almost 40% of field-programmable gate array (FPGA) designers in Europe and supported by the European Space Agency (ESA), UVVM (Universal VHDL Verification Methodology) has been the fastest-growing FPGA verification methodology for the last four years, according to Wilson Research. UVVM provides a test-bench infrastructure, randomization, functional coverage, specification coverage, verification components, scoreboards and more. This allows UVVM users to make structured, readable and reusable testbenches, thus improving quality and speeding up verification.

Embedded systems specialists EmLogic have been running courses on UVVM across the globe for many years. They are now making much of their training material available for universities to use in their education of FPGA designers.

The following modules will be made available to universities, with others potentially being released in due course:

- Basic infrastructure with logging, alert handling, verbosity control, checkers, waiters, etc.

- Bus functional models (BFM): Introduction and advanced use

- Simple, enhanced and optimized randomization

- Functional coverage

You can request access to the UVVM course material by emailing Espen Tallaksen

et@emlogic.no

emlogic.no/uvvm

# Effective testing of cyber-physical systems

Christopher Huth, Bosch Research

Cyber-physical systems, such as control elements in power plants, traffic control systems or vehicles, connect the physical world with the digital world. This interlinking of systems with important infrastructure requires special protection.

Nowadays, safety-critical elements in software development are checked using automated test procedures, as non-automated approaches are too slow and prone to errors with many control elements and complex overall systems. Fuzz testing, in which possible program paths are tested using random inputs and decisions, has become an established technique in this area, particularly for complex software applications (see also 'Coverage-guided fuzzing with virtual ECUs' on p. 12). Compared to alternative test procedures, fuzz testing offers greater efficiency as the complexity of the application increases. The method is therefore also suitable for cyber-physical systems, although it must be adapted to the technical requirements of the systems.

The 'Effective testing of cyber-physical systems' (CPSec) project is researching how fuzz testing can be adapted for embedded cyber-physical systems. Embedded systems are a challenge for researchers as they do not use standardized operating systems and have few input options and interfaces, meaning that they have different requirements for analysis than those of conventional computer systems.

Cyber-physical systems are often characterized by nested program paths that are logically connected to external sensors and actuators. Systematic and in-depth coverage is therefore important to increase quality, speed, and cost efficiency. To this end, static and symbolic analysis methods need to be combined with fuzz testing. The strength of static methods lies in the structured analysis of source code. Symbolic methods simulate the execution of programs and take various program states into account.

The results of CPSec will be used to develop new tools for test generation on all information technology (IT) system layers. These tools will be made available as open-source software and their techniques are documented and evaluated in scientific publications.

The work is funded by the German Federal Ministry of Education and Research (BMBF, project CPSec).

## FURTHER INFORMATION:

[cpsec.io](http://cpsec.io)

CPSEC

# Max Eisele receives ACM Frank Anger Memorial Award 2024

Max Eisele, a research engineer at Bosch, has been honoured with the ACM SIGSOFT Frank Anger Award 2024 for his pioneering work on 'Debugger-driven Embedded Fuzzing'. Presented annually by the Association for Computing Machinery (ACM), this student travel award promotes cross-disciplinary research between embedded systems and software engineering.

Debugger-driven software analysis is a methodology supposed to work on any system or programming language. The key ingredient is utilizing only generic debugging features of widely available debug probes to systematically analyse the system under test during runtime.

Embedded systems, such as those found in medical devices, automotive, and industrial control systems, are increasingly interconnected and vulnerable to cyber-attacks. Eisele's work aims to enhance the security of these systems by identifying potential vulnerabilities before they can be exploited.

Based on the observation that the vast majority of microcontrollers, the brains of any embedded system, provide debug capabilities, debugger-driven fuzzing is applicable at scale. For instance, Eisele showed that the limited number of hardware breakpoints on microcontrollers can be used to obtain partial code coverage feedback that can be used to guide fuzzing. Another approach uses single-stepping and watchpoints to analyse the system under test as it processes input data to learn the input specification, which can then be utilized for model-based fuzzing.

By systematically analysing and identifying potential vulnerabilities in embedded systems, Eisele's research offers a proactive approach to enhancing their security and reliability.

On behalf of HiPEAC, congratulations!

# AIOTI releases paper on edge IoT industrial immersive technologies

The Alliance for IoT and Edge Computing Innovation (AIOTI) Working Group on Research and Innovation has published a paper titled 'Edge IoT Industrial Immersive Technologies and Spatial Computing Continuum, Release 1'. Available for download from the AIOTI website, the paper provides a vision of the convergence of edge internet of things (IoT), artificial intelligence (AI), digital twins, intelligent mesh connectivity, the IoT of senses and spatial computing technologies to create the industrial real-digital-virtual continuum.

In their announcement of the publication of the paper, AIOTI states that the convergence of these technologies into industrial immersive solutions advances the integration and application of edge intelligent immersive technologies combining augmented reality (AR), virtual reality (VR), mixed reality (MR), and extended reality (XR) with concepts like metaverses, omniverse, multiverses, the next-generation spatial web, and web 4.0 as part of future virtual worlds.

AIOTI's position is that this convergence can dramatically transform industrial manufacturing, production operations, training, maintenance, design, collaboration, data visualization, mobility and logistics, improving efficiency, reducing downtime, enhancing safety, and ensuring better decision-making in industrial settings.

However, achieving this convergence results in challenges, including the robustness of hardware, data security, and effective industrial workflow integration.

#### FURTHER INFORMATION:

[bit.ly/AIOTI\\_WG\\_Edge\\_IoT\\_immersive\\_spatial\\_1](https://bit.ly/AIOTI_WG_Edge_IoT_immersive_spatial_1)

## Research on contemporary open-source honeypots

Niclas Ilg, Bosch Research

Threat intelligence is a vital part of any cybersecurity strategy. Web applications, medical devices, automotive connectivity units, or (industrial) internet-of-things (IoT) devices are an entrance into personal and corporate networks. In addition to the rapidly growing number of connected devices and services, machine learning — e.g. in the form of large language models — is expected to shorten the time needed to discover security bugs and zero-day exploits. Whether based on proprietary or open-source software, these applications must be equally secure.

One building block of a successful defence-in-depth strategy is the honeypot, a decoy resource that mimics a valuable target system to entice adversaries. The attacker's strategy and movements on the honeypot system are logged and used to improve existing security measures on genuine devices. In enterprise information technology (IT), honeypots are already an established tool to get early notice of new exploits and zero-day attacks. In addition, the (industrial) IoT domain has also adopted the use of honeypots since botnet variants started attacking its devices on a large scale.

We investigated a large number of honeypots to learn how different solutions seek to deceive potential attackers. The results were published in a comprehensive survey (see 'Further reading', below) and highlight how many different approaches to honeypots there are.

Our research aims to utilize honeypots effectively in the automotive domain. While previous solutions have failed due to the characteristics of the domain (including strict budgets, highly embedded systems with low resources, very limited update capability, and low attacker exposure) we see upcoming electrical / electronic (E/E) architectures as a new chance for successful honeypot deployments. Thus, we consider how honeypots can be an additional layer of intrusion detection inside the vehicle, and how honeypots can be used to learn about novel attack vectors against automotive systems.

#### FURTHER READING:

[doi.org/10.1016/j.jnca.2023.103737](https://doi.org/10.1016/j.jnca.2023.103737)

# Programming Heterogeneous Hardware via Managed Runtime Systems

Authors: Juan Fumero, Athanasios Stratikopoulos and Christos Kotselidis

This book aims to act as an entry point for developers using managed programming languages such as Java and Python to harness accelerators such as graphics processing units (GPUs) for better performance and energy efficiency. It provides an introduction to both heterogeneous execution and managed runtime environments (MREs) by discussing the current trends in computing and the evolution of both hardware and software. To this end, it first details how heterogeneous hardware differs from traditional central processing units (CPUs), what heterogeneous hardware components are and what challenges they pose to heterogeneous execution. Subsequently, current solutions for programming heterogeneous MREs are described, highlighting for each existing solution the associated advantages and disadvantages.

This book is written for scientists and advanced developers who want to understand how choices at the application programming interface (API) level can affect performance and / or programmability of heterogeneous hardware accelerators, how to improve the underlying runtime systems in order to seamlessly integrate diverse hardware resources, and / or how to exploit acceleration techniques from their preferred programming languages.

[bit.ly/Springer\\_Managing\\_Het\\_HW](http://bit.ly/Springer_Managing_Het_HW)

Springer

# TLS Cryptography In-Depth

Explore the intricacies of modern cryptography and the inner workings of TLS

Authors: Paul Duplys and Roland Schmitz

Transport Layer Security (TLS) is the most widely used cryptographic protocol today, enabling e-commerce, online banking, and secure online communication. *TLS Cryptography In-Depth* by Paul Duplys and Roland Schmitz helps you gain a deep understanding of how and why TLS works, how past attacks on TLS were possible, and how vulnerabilities that enabled them were addressed in the latest TLS version 1.3.

Starting with the basic concepts, you'll be led step by step through the world of modern cryptography, guided by the TLS protocol. As you advance, you'll learn about the necessary mathematical concepts from scratch, with even seemingly arcane topics such as public-key cryptography based on elliptic curves explained in terms of real-world applications in TLS. You'll also find out how secret keys are generated and exchanged in TLS, and how they are used to create a secure channel between a client and a server. By the end of this book, you'll have understood the inner workings of TLS and how to configure TLS servers securely, as well as gaining deep knowledge of the cryptographic primitives that make up TLS.

The book was written with two audiences in mind. On one hand, it is written for IT professionals, cybersecurity professionals, security engineers, cryptographers, software developers, and administrators looking to gain a solid understanding of TLS specifics and their relationship with cryptography. On the other hand, it can also be used by computer science and computer engineering students to learn about key cryptographic concepts in a clear, yet rigorous way.

## FURTHER READING:

[bit.ly/Packt\\_TLS\\_Cryptography\\_In-Depth](http://bit.ly/Packt_TLS_Cryptography_In-Depth)

## Dimitris Gizopoulos and collaborators awarded IEEE Transactions on Computers Best Paper Award 2022

HiPEAC member Dimitris Gizopoulos and collaborators have won the best paper award for 2022 from IEEE Transactions in Computing, one of the most prestigious archival journals in computing, for joint work by researchers at the University of Athens, the Universidade Federal do Rio Grande do Sul (UFRGS) and the University of Trento.

The paper, entitled 'Soft Error Effects on Arm Microprocessors: Early Estimations versus Chip Measurements', shows for the first time how early (pre-silicon) estimates (predictions) of central processing unit (CPU) error rates (through detailed microarchitectural injection) in performance simulators (the state-of-the-art in the field: gem5) are correlated to physical error rates obtained from expensive post-silicon accelerated neutron beaming experiments on actual silicon.

Diligently tuned microarchitecture-level fault injection is a powerful approach that saves engineering resources, manufacturing costs, and delivers 'just-right' error protection for CPUs and system-on-chips (SoCs) by identifying the most vulnerable structures of the hardware and the most vulnerable pieces of the software. In the era of large-scale computing in the cloud, edge, and internet of things (IoT), with reports of silent data corruptions (SDCs) compromising datacentre operation, microarchitecture-level reliability assessment of CPUs and SoCs early in the design stages is a valuable piece of the puzzle of implementing robust computing systems.

The paper's journey began with an initial version presented at the IEEE/IFIP International Conference on Dependable Systems and Networks 2019, which was named the best paper runner-up at this top dependability conference. An expanded version of the paper, with

two CPU models and more experimental setups, was then published in IEEE Transactions on Computers in October 2022 and subsequently named best paper for that year; it was that edition's 'Featured Article' and was spotlighted in IEEE Computer journal in its July 2023 issue.

The paper is the result of joint research between Dimitris Gizopoulos' research team at the University of Athens (Computer Architecture Lab, Department of Informatics and Telecommunications), which builds microarchitecture-level reliability assessment methods and tools for heterogeneous SoCs with CPUs, graphics processing units (GPUs), and domain-specific accelerators, and collaborators at the UFRGS and the University of Trento who specialize in beaming. Congratulations to the entire team: Athanasios Chatzidimitriou, George Papadimitriou, Dimitris Gizopoulos (all University of Athens), Paolo Rech (University of Trento), Pablo Rafael Bodmann and Rubens L. Rech Jr (UFRGS).

### FURTHER READING:

P. R. Bodmann, G. Papadimitriou, R. L. R. Junior, D. Gizopoulos and P. Rech. 'Soft Error Effects on Arm Microprocessors: Early Estimations versus Chip Measurements' in *IEEE Transactions on Computers*, vol. 71, no. 10, pp. 2358-2369, 2022

[↗ ieeexplore.ieee.org/document/9616430](https://ieeexplore.ieee.org/document/9616430)

A. Chatzidimitriou, P. Bodmann, G. Papadimitriou, D. Gizopoulos and P. Rech. 'Demystifying Soft Error Assessment Strategies on ARM CPUs: Microarchitectural Fault Injection vs. Neutron Beam Experiments', 2019 49th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Portland, OR, USA, 2019, pp. 26-38

[↗ ieeexplore.ieee.org/document/8809532](https://ieeexplore.ieee.org/document/8809532)

## Lieven Eeckhout wins Computer Architecture Letters Best Paper Award 2022

In related news, HiPEAC member Lieven Eeckhout was awarded the IEEE Computer Architecture Letters Best Paper Award 2022 for his paper 'A First-Order Model to Assess Computer Architecture Sustainability'. Lieven, who gave a keynote talk at the 2024 HiPEAC conference in Munich, has been pioneering the study of sustainability in computer architecture and is an active contributor to the HiPEAC Vision.

### FURTHER READING:

L. Eeckhout, 'A First-Order Model to Assess Computer Architecture Sustainability' in *IEEE Computer Architecture Letters*, vol. 21, no. 02, pp. 137-140, 2022

[↗ bit.ly/L\\_Eeckhout\\_sustainability\\_model](https://bit.ly/L_Eeckhout_sustainability_model)

## ETH Zürich Digital Circuits and Systems Group win tinyML Research Symposium Best Paper Award

The Digital Circuits and Systems Group at ETH Zürich, led by HiPEAC member Luca Benini, received the best paper award at the tinyML Research Symposium 2024. The paper, titled 'Boosting Keyword Spotting through On-Device Learnable User Speech Characteristics', was co-authored by Cristian Cioflan and Lukas Cavigelli.

The paper shows that AI-based speech models can be augmented with simple user features, offering better recognition rates for different accents or voice pitches. This method is suitable for tinyML devices, as it needs only 0.7 mJ of energy to improve the accuracy results by 78% of what training the entire model achieves.

Congratulations on behalf of HiPEAC!

## In memoriam: Detlef Olschewski

In January, we were saddened to hear that HiPEAC member Detlef Olschewski, the chief executive of Cleopa GmbH, had passed away unexpectedly at the age of 54. Detlef was described by his colleagues as someone who brought life, energy, and ingenious ideas to every meeting; who made work feel like home, and who spread humour and positivity everywhere he went.

Our thoughts go out to Detlef's family and friends, who sadly miss him.

## Dates for your diary

### HiPEAC webinars

Check the HiPEAC website to keep up to date on forthcoming dates

↗ [hipeac.net/webinars](https://hipeac.net/webinars)

### HiPEAC 2025: High Performance, Edge And Cloud computing

20-22 January 2025, Barcelona, Spain

Workshop proposal deadline: 1 July 2024

↗ [hipeac.net/2025/barcelona](https://hipeac.net/2025/barcelona)

Sponsorship opportunities available

↗ [sponsorship@hipeac.net](mailto:sponsorship@hipeac.net)

### EPS Summer School 2024

18-23 August 2024, Bertinoro, Italy

↗ [chipsacademy.eu/summer-school](https://chipsacademy.eu/summer-school)

### Euro-Par 2024: 30th International European Conference on Parallel and Distributed Computing

26-30 August 2024, Madrid, Spain

↗ [2024.euro-par.org](https://2024.euro-par.org)

### CPS Summer School

16-20 September 2024, Alghero, Sardinia, Italy

↗ [cpsschooleu](https://cpsschooleu)

### ITEM Workshop 2024: IoT, Edge, and Mobile for Embedded Machine Learning

Co-located with ECML-PKDD 2024

9-13 September 2024, Vilnius, Lithuania

↗ [item-workshop.org](https://item-workshop.org)

### 2024 IEEE Nordic Circuits and Systems Conference (NorCAS)

29-30 October 2024, Lund, Sweden

Paper submission deadline 15 August 2024

↗ [events.tuni.fi/norcas2024](https://events.tuni.fi/norcas2024)

Further information: Jari Nurmi, Tampere University

↗ [norcas@tuni.fi](mailto:norcas@tuni.fi)

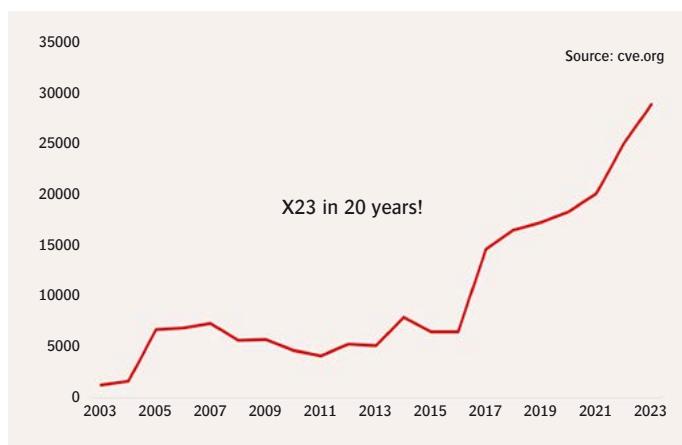

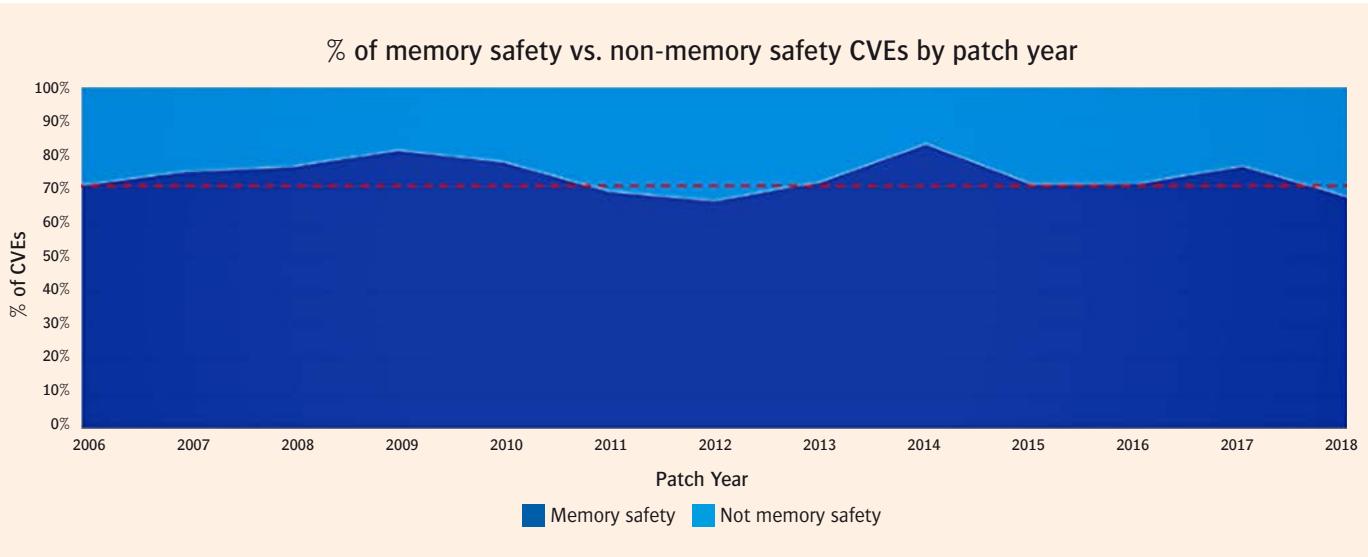

Since 2007, the HiPEAC Vision has considered the topic of cybersecurity, monitoring how increased connectivity and increased reliance on digital technology has resulted in greater vulnerability to cyberattacks. In this article, Olivier Zendra (Inria), a member of the HiPEAC Vision editorial board, sets out some of the main issues for current systems, and for the 'next computing paradigm' to come.

## Threats on the horizon

### Cybersecurity, the 'next computing paradigm' and the HiPEAC Vision

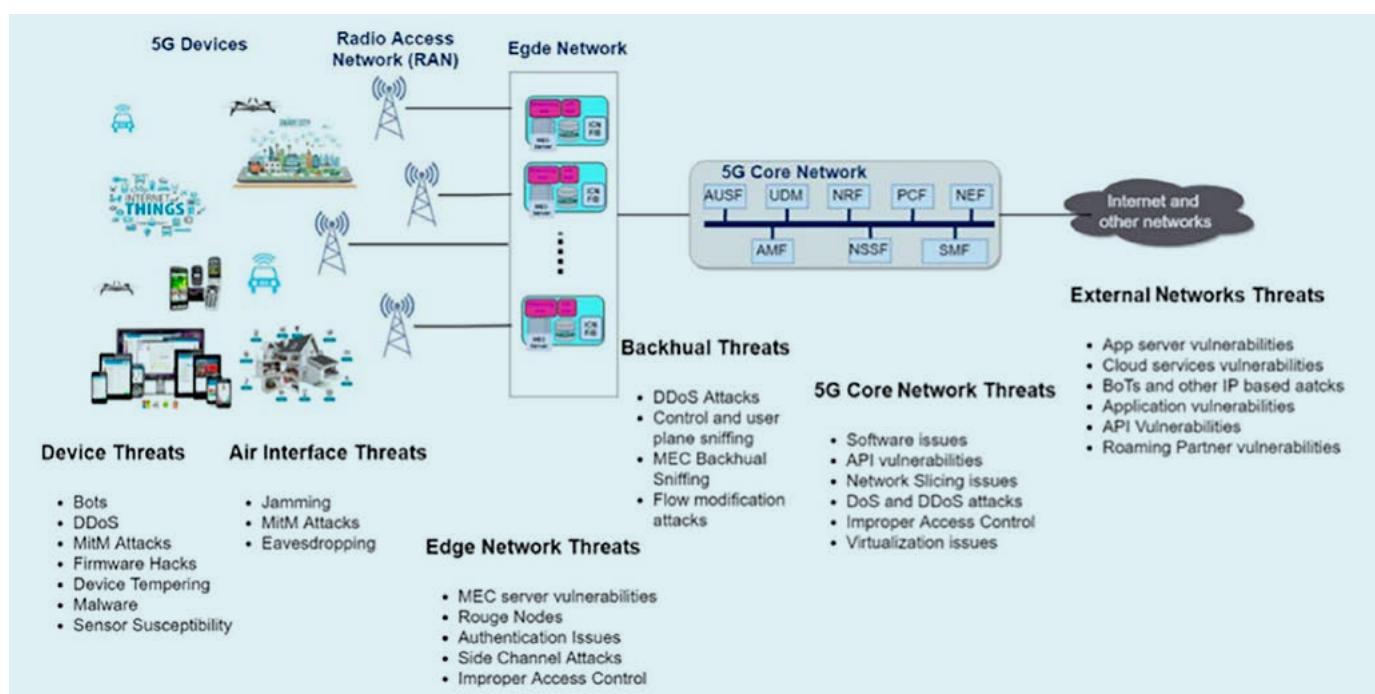

In today's world, where digital technologies are present in almost every area of activity of human life, it is hard to overstate the importance of cybersecurity. Cyberattacks on critical infrastructure, such as manufacturing equipment or power grids, or supply chains, many of which were developed before the most recent digital technologies were available, can have serious, even life-threatening, consequences in the real world. In December 2015, for example, a hack on Ukraine's power infrastructure left 230,000 people without power for several hours. Another striking example is that of healthcare systems, a favourite target for cyberattackers, with a spate of attacks in recent years leading to operational disruption and misery for patients.

One thing that characterizes many of these non high-tech sectors is the use of legacy technology. Manufacturing systems are purchased with the aim of running for decades. One of the main issues in the devastating 2017 WannaCry ransomware attacks on the UK's National Health Service, among others, was the use of legacy operating systems that are no longer supported by the manufacturer.

HiPEAC's vision for the future of computing, the 'next computing paradigm' (NCP), foresees an even greater role for digital technologies, with components dropping seamlessly in and out of the network, and computations taking place across the computing continuum. It envisages even further intertwining of the digital and physical worlds, with the web of humans operating in conjunction with the web of machines.

In practice, this means more connected devices and services, more variety in the kinds of devices and services connected and the kinds of data they share between them, and therefore a considerably increased attack surface. The NCP is more vulnerable to supply-chain attacks due to the multiplication of the components involved, and the large number of composable services creates numerous integration and communication points. The dynamic composition of services offers further attack opportunities.

Another defining characteristic of the NCP is its incorporation of artificial intelligence (AI), from intelligent orchestrators to context adaptation. AI is both a shield and sword in cybersecurity: it can help detect cyberattacks, but could also be used to massively scale up such attacks. Large language models (LLMs) post a whole new area for cybersecurity challenges, such as prompt poisoning, and there is terra incognita ahead. With LLMs available for anyone to access, and increasingly powerful resources being released at incredible speed, cybersecurity approaches will have to adapt to the new AI reality.

No computing system can be accepted without trust, and the NCP is no exception. Hence robust cybersecurity is not optional, which means that the significant challenges in establishing necessary levels of security must be addressed. Individual components need to be assessed on an ongoing basis, but so does the system as a whole. The scale of the challenge is, in fact, enormous, when you start to think of all the points of vulnerability in such a complex digital landscape. One such point would be the communication between devices, for example, bearing in mind how many of today's internet-of-things (IoT) devices are poorly secured.

Another is the software supply chain: contemporary software development encourages the reuse of third-party components, many of them open source, to allow developers to focus on their area of specialization and therefore promote innovation. However, security weaknesses in an extensively used library may impact all systems that use this library. This was demonstrated by the Log4j vulnerability, revealed in December 2021. Rogue developers are another issue; in a recent case, a developer gained the trust of the administrators of the xz compression library, eventually being granted commit access and maintainership – at which point he installed a carefully hidden backdoor. Even hardware is far from immune: malicious integrated circuit alterations can provide hackers with control, while attacks like side-channel analysis allow hackers to obtain data from the system.

Is there light at the end of the tunnel? The decentralization aspect of the NCP offers potential for isolating – and hence protecting – computations, and technologies such as distributed ledger technology (DLT) and the InterPlanetary File System (IPFS) can play a role in decentralization. As witnessed by this magazine's special feature on cybersecurity, and also by the contributions to the HiPEAC Vision, researchers are hard at work on creating defences across the computing stack, from hardware to applications. What is for sure, though, is that making systems more cyber resilient and protecting against attacks has to be a constant, sustained and permanent effort.

### Some common types of cyberattack

- **Malware** (ransomware, spyware, trojans – including hardware trojans)

- **Denial of service (DoS) attacks**, where attackers overwhelm a network with traffic in order to degrade performance or shut down the service. These include battery denial of service attacks, which attempt to drain a device's battery.

- **'Man-in-the-middle' attacks**, where the attacker intercepts communications between two parties while making them believe they are communicating with each other.

- **Social engineering attacks** (phishing, etc.), where attackers impersonate people or services, in order to lure users to give them information, such as passwords, bank details, etc.

*Credit: Arnout Fierens*

### FURTHER READING

HiPEAC Vision 2024

↗ [HiPEAC.net/vision](https://hipecac.net/vision)

Zendra, O., & Coppens, B. (2024). 'The NCP cybersecurity challenges'.

HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10874985](https://doi.org/10.5281/zenodo.10874985)

Coppens, B., & Zendra, O. (2024). 'More data for the NCP implies more privacy risks'. HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10875003](https://doi.org/10.5281/zenodo.10875003)

Rudametkin, W., & Zendra, O. (2024). 'The browser: the key to your privacy on the Web'. HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10875019](https://doi.org/10.5281/zenodo.10875019)

Bertin, E. (2024). 'DLT and IPFS Technologies are Paving the Way for the Next Paradigm in Computing'. HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10875036](https://doi.org/10.5281/zenodo.10875036)

Reimann, L. M., Sisejkovic, D., & Leupers, R. (2024). 'Integrity at Every Link: A Roadmap to Trustworthy Hardware Supply Chains'. HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10875050](https://doi.org/10.5281/zenodo.10875050)

Kunz, W., & Stoffel, D. (2024). 'Microarchitectures as Root-of-Trust in Computing Systems – Research Needs in Formal Security Analysis'.

HiPEAC Vision 2024, Rationale

↗ [doi.org/10.5281/zenodo.10875080](https://doi.org/10.5281/zenodo.10875080)

The expansion of edge computing is posing new challenges for cybersecurity: solutions need to offer robust security with low energy and low latency. To answer this challenge, the NEUROPULS project, funded by the European Union (EU), is taking a novel, neuromorphic approach, developing photonics-based hardware security primitives that draw on the properties of light for robust, yet lightweight, cybersecurity layers. HiPEAC caught up with NEUROPULS coordinator Fabio Pavanello (CNRS – Center for Radiofrequencies, Optics, and Microelectronics in the Alps – CROMA laboratory) to find out more.

# Lighting the way to better security

## The NEUROPULS photonics-based approach

### *What's wrong with the current security landscape?*

The exponentially increasing number of edge devices is posing major challenges not only on the computing side, in terms of processing requirements, but also in terms of cybersecurity. The available surface for cyberattacks increases with the number of interconnected devices, as do the complexity and latency of authentication and encryption protocols. Current solutions that rely on, for example, storing cryptographic keys in non-volatile memory are not secure enough. As an example, hardware vulnerabilities can be leveraged to access specific memory sectors, and approaches based purely on electronic hardware security primitives present a series of weaknesses, such as being prone to machine-learning (ML) modelling and side-channel attacks, or reliability issues due to the ageing of key components, for example.

### *That doesn't sound good...*

No, especially when you consider that applications in sectors such as banking, manufacturing, automotive and healthcare cannot function without robust cybersecurity.

*Achieving robust cybersecurity isn't that simple, though, right?*

Exactly. In addition to being robust to cyberthreats and reliable, security layers also need to be low power, lightweight, and low cost for large-volume applications. All these requirements set severe constraints on both the hardware and software layers of these devices, meaning that we need to develop unconventional cybersecurity approaches with superior robustness compared to current solutions.

### *So what's NEUROPULS doing about it?*

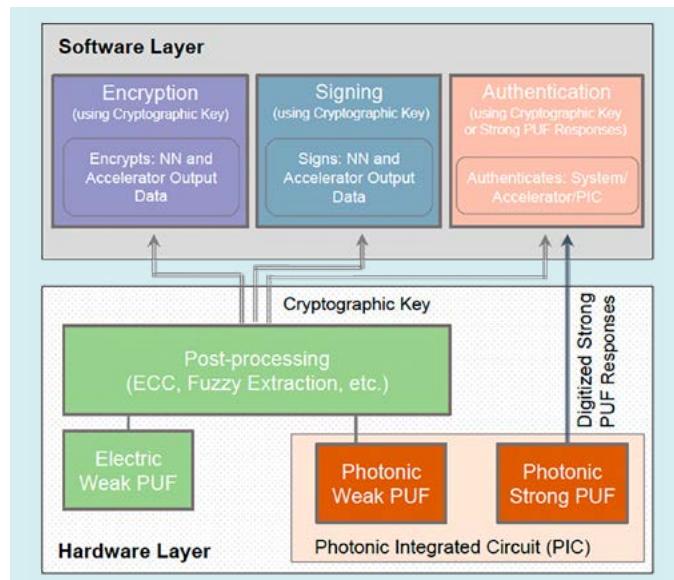

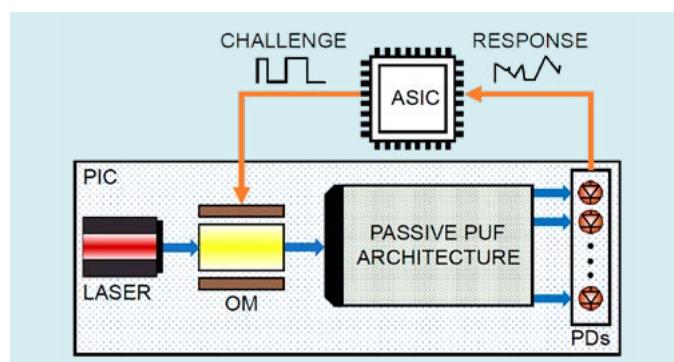

Adopting a neuromorphic approach, which saves energy, avoiding the input / output bottleneck between memory and processing units, and which supports machine-learning (ML) algorithms, NEUROPULS targets the secure operation, communication, and integrity of edge devices. We're building security layers starting

with hardware security primitives, using the unique technology developed in the project based on augmented silicon photonics platforms. This technology is readily available for our photonic accelerator, which is co-developed in the same photonic integrated circuit (PIC) as the security primitives. These primitives are the key ingredient of our approach and are based on photonic physical unclonable functions (PUFs), which have the potential for better performance compared to their electronic counterparts.

### *What gives photonics an advantage over electronics in this area?*

The enhanced strength of our approach comes from the underlying physics of such complex photonic devices, which provide many degrees of freedom that can be exploited, making it more robust against ML or side-channel attacks. This is in stark contrast with electronic approaches, where essentially information propagates in a binary manner, thus leading to lower system complexity overall and thus potential vulnerabilities for various types of attacks.

In the software layer, we can then leverage key properties of photonic PUFs, such as high operation speed (Gbit/s) to enable lightweight security protocols. For example, a lightweight remote software attestation mechanism periodically ensures that the device has not been tampered with, protecting against unauthorized software, particularly malware, malicious software modifications and associated risks, by using the photonic PUF as the root of trust.

### *Any other cybersecurity protections?*

We also use encryption to protect sensitive neural-network information such as weight values and data in input / output, as well as to secure communication with third parties using the error-corrected keys generated by the photonic PUF. Finally, various lightweight authentication protocols are under investigation in the NEUROPULS project to assess the genuine identity of a given device within the network without requiring fully stable PUF responses.

What are the particular challenges of ensuring robust security for edge computing? I assume energy is going to be at a premium, for example...

Precisely: in edge computing, the main goal is to securely process substantial amounts of data close to where these data are generated. This means that you need lightweight accelerators that can deal with massive amounts of data using little energy and with low latency, while also being protected by robust security layers. To address this problem, NEUROPULS takes advantage of the properties of light and of materials such as phase-change materials (PCMs), as well as III-V materials, to develop an ultra-low-power (sub-pJ/MAC) accelerator which at the same time presents highly robust security layers.

Sounds groundbreaking – but how would it work with existing systems?

We are co-developing processor interfaces for seamless integration in current systems. We're using RISC-V core architectures to drive our accelerator, which allow us to develop a prototype without licensing constraints. In parallel, a gem5-based simulation platform

is under development to enable accelerator scaling and performance profiling, while incorporating the novel security layers.

I'm sold. What are the next steps towards commercialization, and how could this technology change the current cybersecurity landscape?

We aim to bring this technology, which is still at the proof-of-concept phase, to a much more mature technology readiness level. This would make it a realistic, scalable alternative to current insecure, power-hungry solutions for edge computing applications.

The advent of novel security primitives such as PUFs based on photonics rather than more conventional CMOS technologies, coupled with protocols which exploit their unique properties, could affect the overall supply chain and penetrate market segments that have so far been dominated by electronic solutions. This would allow us to build edge devices and sub-systems that are far more resilient to cyberthreats and fluctuations. For example, safety-critical applications such as autonomous driving could greatly benefit from security layers that outperform current solutions and that are integrated into low-power and low-latency photonic accelerators.

[neuropuls.eu](http://neuropuls.eu)

NEUROPULS has received funding from the European Union's Horizon Europe research and innovation programme under grant agreement no. 10170238. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

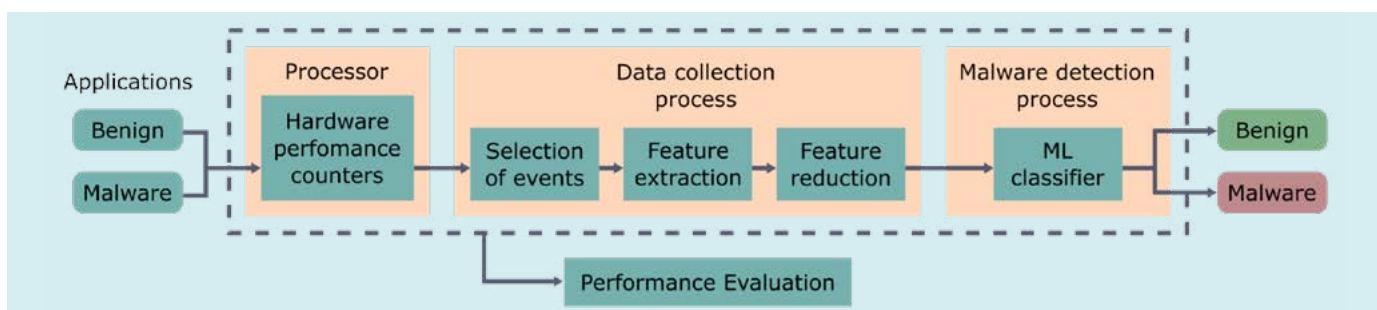

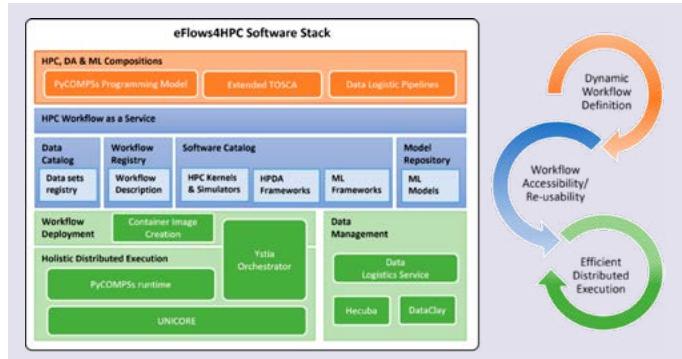

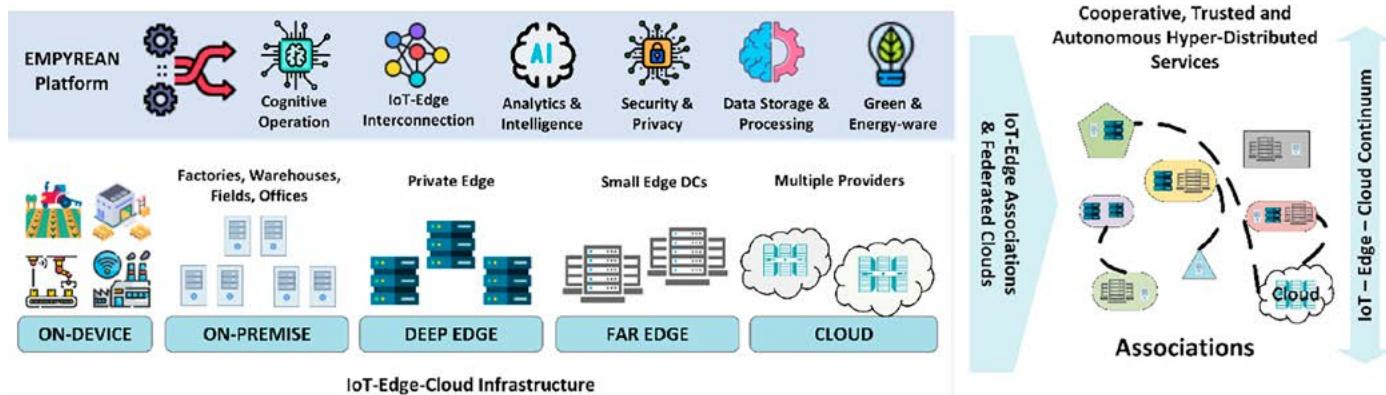

#### FURTHER READING: