Inspiration

Timing closure is the #1 bottleneck in FPGA and ASIC design, costing engineers months of effort and millions in project delays. We wanted to build a tool that could make timing closure as easy as spellcheck—turning cryptic timing reports into actionable, human-readable fixes in seconds. Cerebras’ blazing-fast AI inference and structured output capabilities inspired us to reimagine timing analysis as an AI-first workflow, not just a manual debugging chore.

What it does

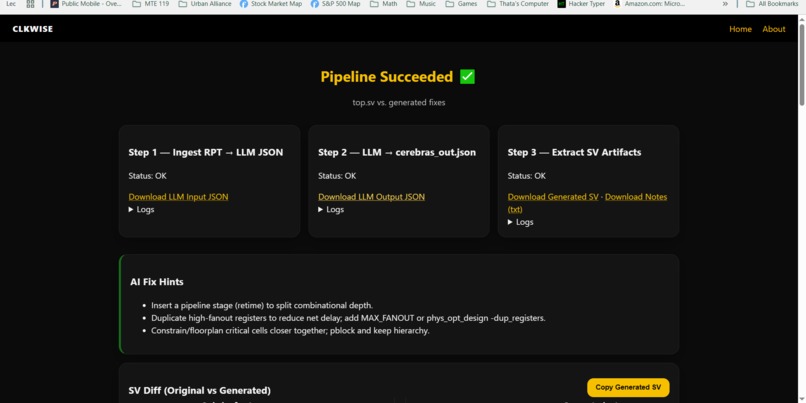

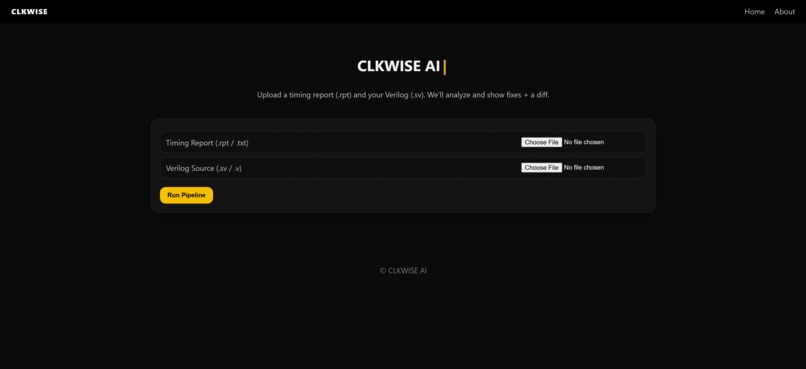

Clkwise AI is the world’s first AI-powered FPGA timing debugger. Upload your Vivado timing report and Verilog source, and Clkwise instantly analyzes the design using a dual-AI pipeline powered by Cerebras. It identifies root causes of timing violations, explains them in plain English, and generates step-by-step, context-aware code fixes—complete with a visual diff and copy-to-clipboard functionality for the new Verilog. Engineers get not just suggestions, but real, validated code changes and confidence metrics.

How we built it

We built a full-stack web app using Flask (Python) for the backend and a modern, responsive frontend. The core innovation is our dual-AI pipeline:

- Cerebras: We leveraged Cerebras’ LLMs for ultra-fast, structured analysis of massive timing datasets. Cerebras parses the timing report, extracts critical paths, root causes, and generates a JSON summary of issues and recommended fixes.

- Cohere: For deep synthesis and natural language explanations, we used Cohere’s models to turn technical data into clear, actionable advice.

- Pipeline: The backend orchestrates file uploads, runs the analysis scripts, and extracts AI-generated code patches. The frontend displays diffs, fix hints, and enables one-click copying of the generated Verilog. ## Challenges we ran into

- Parsing complexity: Vivado timing reports are huge and inconsistent. Building robust parsers and aligning them with Cerebras’ expected input schema was a major challenge.

- AI integration: Getting Cerebras to output not just text, but structured, actionable JSON (with code patches and rationale) required careful prompt engineering and schema validation.

- Latency: We optimized the pipeline to keep total analysis time under 2 seconds, leveraging Cerebras’ speed for the heavy lifting.

- User experience: Presenting complex timing data and code diffs in a way that’s intuitive for hardware engineers took several UI/UX iterations. ## Accomplishments that we're proud of

- End-to-end automation: From raw timing report to actionable code diff, all in one click.

- Cerebras-powered analysis: We demonstrated how Cerebras’ LLMs can be used for structured, domain-specific reasoning—not just chat.

- Real code generation: The system produces Verilog code patches that can be directly copy-pasted or downloaded, accelerating the timing closure loop.

- Industry relevance: Our approach is validated by real-world timing reports and expert heuristics. ## What we learned

- AI for EDA is here: With the right prompts and schema, LLMs like Cerebras can reason about hardware, not just software.

- Structured output is key: For engineering workflows, AI needs to output data, not just prose. Cerebras’ ability to generate JSON summaries and code blocks was a game-changer.

- User trust matters: Engineers want to see not just what to change, but why. Providing rationale and confidence scores builds trust in AI-driven suggestions. ## What's next for Clkwise AI

- Deeper Cerebras integration: We plan to expand our use of Cerebras for even faster, more granular timing analysis and to support more EDA toolchains.

- Simulation and verification: Integrate waveform and simulation checks to validate AI-generated fixes.

- Enterprise features: Add team collaboration, project history, and API endpoints for CI/CD integration.

- Broader hardware support: Extend to ASIC flows, more FPGA vendors, and custom timing constraints.

- Community and feedback: Launch a beta program with real hardware teams to refine and expand Clkwise’s capabilities. Clkwise AI is just the beginning—thanks to Cerebras, we’re making timing closure intelligent, explainable, and lightning-fast.

Challenges We Ran Into

- Parsing complexity: Vivado timing reports are huge and inconsistent. Building robust parsers and aligning them with Cerebras’ expected input schema was a major challenge.

- AI integration: Getting Cerebras to output not just text, but structured, actionable JSON (with code patches and rationale) required careful prompt engineering and schema validation.

- Latency: We optimized the pipeline to keep total analysis time under 2 seconds, leveraging Cerebras’ speed for the heavy lifting.

- User experience: Presenting complex timing data and code diffs in a way that’s intuitive for hardware engineers took several UI/UX iterations.

Accomplishments That We're Proud Of

- End-to-end automation: From raw timing report to actionable code diff, all in one click.

- Cerebras-powered analysis: We demonstrated how Cerebras’ LLMs can be used for structured, domain-specific reasoning—not just chat.

- Real code generation: The system produces Verilog code patches that can be directly copy-pasted or downloaded, accelerating the timing closure loop.

- Industry relevance: Our approach is validated by real-world timing reports and expert heuristics.

What We Learned

- AI for EDA is here: With the right prompts and schema, LLMs like Cerebras can reason about hardware, not just software.

- Structured output is key: For engineering workflows, AI needs to output data, not just prose. Cerebras’ ability to generate JSON summaries and code blocks was a game-changer.

- User trust matters: Engineers want to see not just what to change, but why. Providing rationale and confidence scores builds trust in AI-driven suggestions.

What's Next for Clkwise AI

- Deeper Cerebras integration: We plan to expand our use of Cerebras for even faster, more granular timing analysis and to support more EDA toolchains.

- Simulation and verification: Integrate waveform and simulation checks to validate AI-generated fixes.

- Enterprise features: Add team collaboration, project history, and API endpoints for CI/CD integration.

- Broader hardware support: Extend to ASIC flows, more FPGA vendors, and custom timing constraints.

- Community and feedback: Launch a beta program with real hardware teams to refine and expand Clkwise’s capabilities.

Deeper Cerebras Integration: Real-Time Timing Closure

Timing closure in FPGA/ASIC design is a notorious bottleneck — each iteration of parsing timing reports, diagnosing, applying RTL fixes, and rerunning tools can take hours. Our project integrates Cerebras inference to break this cycle and deliver a new class of workflow:

- Real-time analysis: Parse and summarize thousands of timing paths per second.

- Agentic exploration: Simulate hundreds of RTL edits in parallel, recommending the most promising fixes.

- Cross-toolchain support: Works across Vivado, Quartus, Synopsys, and Cadence.

- Conversational feedback: At 3,000 tokens/sec, engineers can “chat” with their design:

“Your worst path is 7.6ns; inserting a pipeline stage here reduces 3 levels of logic.”

This directly showcases what becomes possible when inference is no longer the bottleneck: static reports become interactive sessions, engineers gain agentic co-pilots, and timing closure transforms from a slow slog into a real-time design experience. Perfectly aligned with the Best Use of Cerebras track.

Log in or sign up for Devpost to join the conversation.