# PicoGRAM: Practical Garbled RAM from Decisional Diffie-Hellman

Tianyao Gu<sup>1,2</sup>, Afonso Tinoco<sup>1,2,3</sup>, Sri Harish G Rajan<sup>1</sup>, and Elaine Shi<sup>1,2</sup>

<sup>1</sup>Carnegie Mellon University

<sup>2</sup>Oblivious Labs, Inc.

<sup>3</sup>Instituto Superior Técnico

August 14, 2025

## Abstract

Making 2-party computation scale up to big datasets is a long-cherished dream of our community. More than a decade ago, a line of work has implemented and optimized interactive RAM-model 2-party computation (2PC), achieving somewhat reasonable concrete performance on large datasets, but unfortunately suffering from  $\tilde{O}(T)$  roundtrips for a  $T$ -time computation. Garbled RAM promises to compress the number of roundtrips to 2, and encouragingly, a line of recent work has designed concretely efficient Garbled RAM schemes whose asymptotic communication and computation costs almost match the best known interactive RAM-model 2PC, but still leaves  $(\text{poly}) \log \log$  gaps.

We present PicoGRAM, a practical garbled RAM (GRAM) scheme that not only asymptotically matches the prior best RAM-model 2PC, but also achieves an *order of magnitude* concrete improvement in *online* time relative to interactive RAM-model 2PC, on a dataset of size 8GB. Moreover, our work also gives the first Garbled RAM whose total cost (including bandwidth and computation) achieves an optimal dependency on the database size (up to an arbitrarily small super-constant factor).

Our work shows that for high-value real-life applications such as Signal, blockchains, and Meta that require oblivious accesses to large datasets, Garbled RAM is a promising direction towards eventually removing the trusted hardware assumption that exists in production implementations today. Our open source code is available at <https://github.com/picogramimpl/picogram>.

# Contents

|          |                                                                       |           |

|----------|-----------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                   | <b>4</b>  |

| 1.1      | Our Theoretical Contribution . . . . .                                | 4         |

| 1.2      | Open-Source Implementation and Concrete Performance . . . . .         | 5         |

| 1.3      | Technical Highlight . . . . .                                         | 7         |

| 1.4      | Additional Related Work . . . . .                                     | 8         |

| <b>2</b> | <b>Roadmap</b>                                                        | <b>8</b>  |

| 2.1      | Background: Tri-State Circuits and Inefficient Strawman . . . . .     | 8         |

| 2.2      | Our Blueprint: Extending Tri-State Circuits with SIMD Gates . . . . . | 12        |

| 2.3      | Garbling SIMD Tri-State Circuits . . . . .                            | 13        |

| 2.4      | Efficient Garbled Stack . . . . .                                     | 15        |

| <b>3</b> | <b>Computational Model: SIMD Tri-State Circuits</b>                   | <b>15</b> |

| 3.1      | Definitions . . . . .                                                 | 15        |

| 3.2      | Operational Semantics . . . . .                                       | 16        |

| <b>4</b> | <b>Garbling SIMD Tri-State Circuits</b>                               | <b>18</b> |

| 4.1      | Definitions . . . . .                                                 | 18        |

| 4.2      | Our Construction from DDH . . . . .                                   | 19        |

| 4.3      | Analysis . . . . .                                                    | 22        |

| <b>5</b> | <b>From Garbled SIMD Tri-State Circuit to Garbled RAM</b>             | <b>26</b> |

| 5.1      | Oblivious Simulation of RAM in SIMD Tri-State Circuit . . . . .       | 26        |

| 5.2      | Garbled RAM Construction . . . . .                                    | 27        |

| 5.3      | GRAM Cost Analysis . . . . .                                          | 27        |

| <b>6</b> | <b>Concretely Efficient Stack</b>                                     | <b>28</b> |

| 6.1      | Syntax: Compaction Stack and Distribution Stack . . . . .             | 28        |

| 6.2      | Stack Constructions from Oblivious Compaction . . . . .               | 28        |

| <b>7</b> | <b>Evaluation</b>                                                     | <b>32</b> |

| <b>A</b> | <b>Deferred Cost Analysis</b>                                         | <b>42</b> |

| A.1      | Handling Cases $T > N$ and $T < N$ . . . . .                          | 42        |

| A.2      | Improving Dependence on the $\omega(1)$ Factor . . . . .              | 42        |

| A.3      | Final Cost Analysis . . . . .                                         | 43        |

| <b>B</b> | <b>Deferred Analysis of Improved Stack Circuitry</b>                  | <b>44</b> |

| B.1      | Preliminaries . . . . .                                               | 44        |

| B.2      | Analysis of Eager-Prefix-Sum . . . . .                                | 45        |

| B.3      | Analysis of SIMD Stack . . . . .                                      | 48        |

| B.4      | Analysis of Compaction and Distribution Stack . . . . .               | 50        |

| <b>C</b> | <b>Garbling SIMD Tri-State Circuits in Random Oracle Model</b>        | <b>52</b> |

| C.1      | Our Construction from DDH and Random Oracle . . . . .                 | 53        |

| C.2      | Analysis . . . . .                                                    | 54        |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>D Additional Concrete Optimizations</b>                         | <b>61</b> |

| D.1 Optimizing Cryptographic Primitives . . . . .                  | 61        |

| D.2 Optimizing and Parallelizing Group Operations . . . . .        | 64        |

| D.3 Circuit-level Optimizations . . . . .                          | 64        |

| D.4 Parameter Tuning. . . . .                                      | 65        |

| <b>E Remarks on Concrete Performance of Baselines</b>              | <b>65</b> |

| E.1 Comparing NanoGRAM and TSC . . . . .                           | 65        |

| E.2 EpiGRAM and VISAs . . . . .                                    | 66        |

| E.3 Additional Comparison with Interactive RAM-model 2PC . . . . . | 66        |

# 1 Introduction

Garbled circuits, first introduced by Yao [Yao86], are a fundamental cryptographic tool for constant-round secure two-party computation (2PC). Despite decades of optimizations that have made garbled circuits practical [BMR90, NPS99, KS08, ZRE15, RR21, BHKR13, HEKM11, SHS<sup>+</sup>15], most works focus on Boolean circuit computation and fail to efficiently capture the Random Access Machine (RAM) model, which is ubiquitous in real-world computation. A RAM with space  $N$  features a constant number of registers and a memory of  $N$  cells, where each register or memory cell can store a  $W$ -bit word. In every time step, the RAM performs a CPU instruction over the registers' values, as well as a memory read and write operation.

While CPU instructions can be garbled efficiently as Boolean circuits, garbling memory accesses presents greater challenges. The naïve approach is to convert each memory read and write into a circuit that linearly scans through memory, resulting in prohibitive overhead as the data size grows.

There are two main approaches to avoid this per-instruction linear scan overhead. First, a line of work has shown how to achieve (interactive) RAM-model 2PC [GKK<sup>+</sup>12, GGH<sup>+</sup>13b, WHC<sup>+</sup>14, ZWR<sup>+</sup>16, DS17, WCS15, LHS<sup>+</sup>14, LWN<sup>+</sup>15]. State-of-the-art constructions [WCS15, LWN<sup>+</sup>15, Kel20] in this literature typically use Circuit ORAM [WCS15] to convert the RAM to a sequence of interactive circuits, and then use a 2PC protocol (e.g., garbled circuits) to evaluate them. When the word size  $W$  is at least  $\Omega(\log^2 N)$ , the resulting 2PC protocol achieves a per-instruction communication cost of  $O(\lambda \cdot W \cdot \log N \cdot \omega(1))$ , where  $\omega(1)$  is an arbitrarily small super-constant function in the RAM's space  $N$ , but suffers from  $\tilde{O}(T)$  rounds, where  $T$  is the running time of the original RAM [WCS15]. The large round complexity makes this approach unsuitable for deployments with high end-to-end latency (e.g., over a wide-area network), especially when  $T$  is large.

The second approach is to use an efficient garbled RAM (GRAM) [LO13] scheme. Like garbled circuits, a garbled RAM requires only two rounds when used in a semi-honest 2PC protocol. However, unlike the naïve approach of converting each memory access into a linear scan, garbled RAM significantly reduces the per-instruction cost to polylogarithmic in  $N$ . A key challenge is designing a concretely efficient garbled RAM scheme. Unfortunately, earlier works in this literature [LO13, GHL<sup>+</sup>14, GLO15, GLOS15, LO17] focused only on theoretical feasibility, without explicitly quantifying the poly factor in the poly log overhead. While recent works [HKO22, PLS23, HKO23] have made encouraging progress in minimizing the poly log factor, their communication and computation costs are still a (poly) log log factor away from the prior best interactive RAM-model 2PC [WCS15, LWN<sup>+</sup>15].

## 1.1 Our Theoretical Contribution

We propose a new garbled RAM construction called PicoGRAM. We reduce the extra poly log log  $N$  factor in previous constructions [PLS23, HKO23] to an arbitrarily small super-constant factor, leveraging the Decisional Diffie-Hellman (DDH) assumption. For word size  $W = \Omega(\log^2 N)$ , PicoGRAM achieves a per-instruction communication cost of  $O(\lambda \cdot W \cdot \log N \cdot \omega(1))$ , where we abuse the  $\omega(1)$  notation to mean an arbitrarily small super-constant function in  $N$ . In this sense, PicoGRAM matches the communication cost of the best known RAM-model 2PC scheme [WCS15]<sup>1</sup>, but we reduce the round complexity from  $\tilde{O}(T)$  to only two rounds.

---

<sup>1</sup>Since we care about concrete efficiency, we compare only with concretely efficient constructions. The line of work on succinct garbled RAM [LP14, BGL<sup>+</sup>15, CHJV15, KLW15, CCHR16, CH16, CCC<sup>+</sup>16, ACC<sup>+</sup>16, AL18] is asymptotically better but completely impractical due to their reliance on indistinguishability obfuscation [JLS20, GGH<sup>+</sup>13a]. See Section 1.4 for more discussion.

Table 1: Comparison of communication cost with prior works for semi-honest 2PC, where  $N$  is the RAM’s space,  $T$  is the RAM’s runtime, and  $W$  is the word width. OWF stands for one-way functions and CCRH stands for circular correlation robust hash. Interactive represents the RAM-model 2PC construction in the work of Circuit ORAM [WCS15].

|                     | Comm. in bits per instruction                                        | Rounds              | Assumption |

|---------------------|----------------------------------------------------------------------|---------------------|------------|

| Interactive [WCS15] | $O(\lambda \cdot (W \cdot \log N \cdot \omega(1) + \log^3 N))$       | $O(T \cdot \log N)$ | OWF        |

| EpiGRAM [HKO22]     | $O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot \log N)$          | 2                   | CCRH       |

| NanoGRAM [PLS23]    | $O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot (\log \log N)^2)$ | 2                   | CCRH       |

| Tri-State [HKO23]*  | $O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot \log \log N)$     | 2                   | OWF        |

| PicoGRAM            | $O(\lambda \cdot (W \cdot \log N \cdot \omega(1) + \log^3 N))$       | 2                   | DDH        |

\* While tri-state GRAM [HKO23, Hea24] presents their results assuming  $N = T$ , we show in Section A.1 that this assumption can be removed.

A more generalized version of our asymptotic result is stated in the following theorem, where communication is measured in bits, and computation is measured in terms of group multiplications.

**Theorem 1.1.** *Assume the Decisional Diffie-Hellman (DDH) assumption. There exists a garbled RAM with an amortized communication and computation cost of  $O(\lambda \cdot (W \cdot \log N \cdot \omega(1) + \log^3 N))$  per instruction, where  $N$  is the RAM’s space (counted in the number of words),  $W$  is the word width,  $\lambda$  is the security parameter, and  $\omega(1)$  is an arbitrarily small super-constant factor in  $N$ .*

For both the RAM-model 2PC literature [WCS15, LWN<sup>+</sup>15, Kel20] and PicoGRAM, the extra  $\omega(1)$  factor stems from the underlying ORAM construction [WCS15], and it is an open question whether we can eliminate it while still preserving concrete efficiency. Even the more restricted problem of devising a concretely efficient Oblivious RAM scheme (suitable for garbled RAM or 2PC) without the extra  $\omega(1)$  factor remains open.

We give a more detailed comparison with prior work in Table 1. Note that in PicoGRAM, the security parameter  $\lambda$  denotes the number of bits used to represent a group element, whereas in other schemes  $\lambda$  denotes the number of bits of a one-way function or a circular correlation robust hash (CCRH) [KS08, CKZ12].

## 1.2 Open-Source Implementation and Concrete Performance

**Open-source implementation.** Although Theorem 1.1 can be based solely on the DDH assumption, for our practical implementation, we additionally adopt FreeXOR-style optimizations [KS08, RR21] for better concrete performance. Therefore, our practical variant of PicoGRAM additionally relies on the existence of a random oracle (RO) for these concrete optimizations to work. We implemented this practical variant in C++ and open-sourced the code at <https://github.com/picogramimpl/picogram>.

For our current implementation, we store all the garbled circuitry in memory. For this reason, in our evaluation results later, all results for up to  $N = 2^{16}$  are from actual measurements, whereas results for larger  $N$  are extrapolated. Note that reported communication costs are exact regardless of  $N$ , since communication costs can be calculated in “count mode” (i.e., a simulator that does not actually execute the cryptography). With some extra engineering work, it is not too hard to extend our current implementation with a better memory management scheme. Using appropriate pipelining, we expect that the memory management should not incur noticeable slowdown, so our extrapolated numbers for  $N > 2^{16}$  should be quite accurate.

Table 2: Comparison of concrete costs with prior works for semi-honest 2PC, assuming a word width of 64 bits, network bandwidth of 300 Mbps, and a round trip time of 100 ms.  $N$  is the RAM’s space. Every column represents a different variant of each scheme optimized for the corresponding metric. The results for  $N = 2^{30}$  are extrapolated.

| Scheme                              | $N$      | Communication |                         | End-to-end Time |                         | Online Time |                         |

|-------------------------------------|----------|---------------|-------------------------|-----------------|-------------------------|-------------|-------------------------|

|                                     |          | MB            | Relative to Interactive | ms              | Relative to Interactive | ms          | Relative to Interactive |

| Interactive [WCS15]                 | $2^{16}$ | <b>2.94</b>   | <b>1</b> ×              | 378             | 1×                      | 102         | 1×                      |

|                                     | $2^{30}$ | <b>13.1</b>   | <b>1</b> ×              | 1365            | 1×                      | 455         | 1×                      |

| Prior-best<br>GRAM [PLS23]          | $2^{16}$ | 16.4          | 5.58×                   | 490             | 1.30×                   | 30.9        | 0.30×                   |

|                                     | $2^{30}$ | 120           | 9.16×                   | 3565            | 2.61×                   | 220         | 0.48×                   |

| PicoGRAM<br>(tuned for each metric) | $2^{16}$ | 3.94          | 1.34×                   | <b>156</b>      | <b>0.41</b> ×           | <b>9.73</b> | <b>0.095</b> ×          |

|                                     | $2^{30}$ | 18.5          | 1.41×                   | <b>600</b>      | <b>0.44</b> ×           | <b>41.0</b> | <b>0.090</b> ×          |

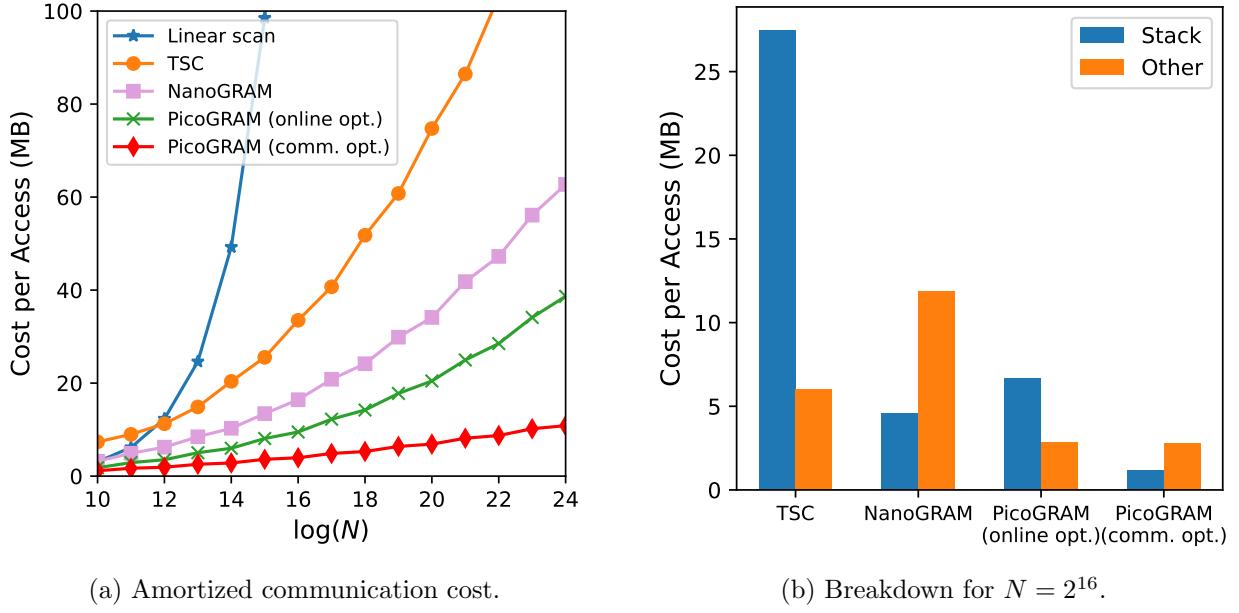

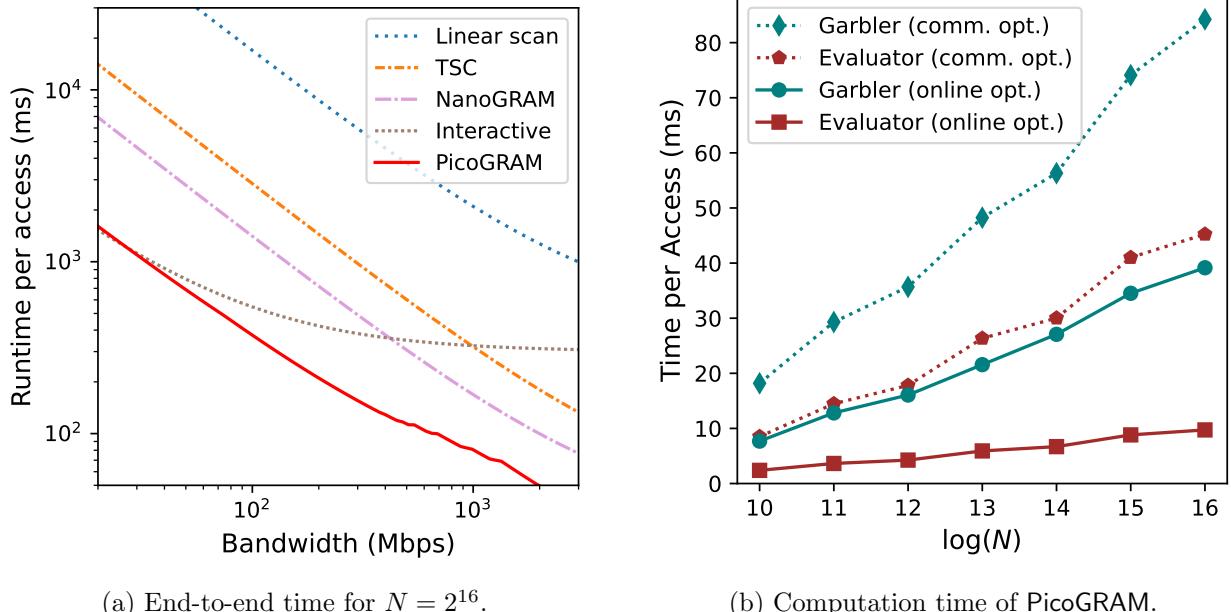

**Concrete performance.** We evaluated the concrete performance of PicoGRAM. In Table 2, we compare PicoGRAM’s performance with two baselines: 1) state-of-the-art RAM-model 2-party computation [WCS15, LWN<sup>+</sup>15] (also called the “interactive” baseline), and 2) state-of-the-art Garbled RAM [PLS23]. The metrics we focus on include the communication cost, the end-to-end time, and the online time. Note that when reporting each metric, we are using a different variant of the scheme specifically optimized for the metric of concern.

Making RAM-model 2-party computation (2PC) practical for big data has been a long-cherished dream of our community. Table 2 shows that excitingly, standing on the shoulders of recent efforts [HKO22, PLS23, HKO23], practical Garbled RAM can finally beat the interactive baseline [WCS15, LWN<sup>+</sup>15] in terms of both overall time and online time! Specifically, relative to the prior best interactive baseline, although PicoGRAM incurs 34% to 41% more communication, it achieves roughly **2.3**× and **11**× improvement in overall time and online time, respectively. Compellingly, since PicoGRAM compresses the round complexity to two, all the garbling and transmission of the garbled circuitry can be now performed offline. Therefore, in applications where the online response time is critical, PicoGRAM has a significant advantage over the interactive baseline.

Relative to the prior best Garbled RAM, PicoGRAM achieves **4.2 - 6.5**× improvement in communication, **3.1 - 5.9**× improvement in overall time, and **3.2 - 5.4**× improvement in online time. Note that we use NanoGRAM [PLS23] as the baseline here since its concrete performance is better than tri-state [HKO23] and VISAs [YPHK23] (despite being asymptotically slightly worse than tri-state).

**Comparison with “ORAM + trusted hardware” and PIR.** Today, real-life applications that require privately accessing large datasets such as Signal’s private contact discovery [sig], oblivious accesses to blockchain data [olab], and Meta [met] settle for an “trusted hardware + ORAM” solution, not because people believe trusted hardware to be bullet-proof, but more as a near-term compromise in exchange for its fast performance and the ability to support general computation. However, many industry leaders want to remove the trusted hardware assumption, and are thus eyeing a cryptography-based solution for the medium to longer term.

As a reality check, the state-of-the-art “trusted hardware + ORAM” solution [olaa] can support a single key-value look up in  $20 - 50\mu\text{s}$  for a database of  $N = 2^{16}$  to  $N = 2^{30}$  with 64-byte records. A state-of-the-art Private Information Retrieval (PIR) scheme can achieve roughly 12ms online computation and 100ms overall time for a database of size roughly 100GB [ZPSZ24] (assuming about 60ms ping latency). Besides Garbled RAM, PIR is another promising approach for removing

the trusted hardware. However, although state-of-the-art PIR schemes [ZPSZ24] enjoy similar online time as PicoGRAM, they suffer from the following drawbacks relative to PicoGRAM [Shi25]:

1. So far, practical PIR cannot support generic computation, which makes it difficult for software maintenance and updates. The more general form that supports generic computation called RAM-model FHE [LMW23] remains in theory land.

2. So far, practical PIR schemes are in the so-called client-preprocessing model [CHK22, ZPSZ24], which makes it challenging to deploy in scenarios with fast-evolving databases.

Therefore, in summary, our work suggests that practical Garbled RAM is a promising direction towards eventually removing the trusted hardware in high-value applications such as Signal, blockchains, and Meta, while retaining the generality and relative ease of software updates.

### 1.3 Technical Highlight

**Inefficiencies in existing garbled RAM.** First, there remains an asymptotic gap to optimality. Recent works [PLS23, HKO23], including NanoGRAM [PLS23] and tri-state GRAM [HKO23], achieve a per-instruction communication cost of  $O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot \text{poly log log } N)$  bits, where  $N$  is the RAM’s space,  $W$  is the word width, and  $\lambda$  is the security parameter. For word size  $W = \Omega(\log^2 N)$ , the cost simplifies to  $O(\lambda \cdot W \cdot \log N \cdot \text{poly log log } N)$ , which remains a  $\text{poly log log } N$  factor away from optimality in  $N$  due to known logarithmic Oblivious RAM lower bounds [GO96, BN16, LN18, PLS23].

Second, although known garbled RAM schemes reduce the round complexity to two, they fail to match the best known RAM-model 2PC schemes [WCS15, Kel20] in terms of communication cost (i.e., the number of bits transmitted). As mentioned, state-of-the-art RAM-model 2PC achieves a per-instruction communication cost of  $O(\lambda \cdot W \cdot \log N \cdot \omega(1))$  for sufficiently large words, and the best known garbled RAMs [PLS23, HKO23] are a  $\text{poly log log}$  factor worse. For example, for  $N = 2^{20}$ , tri-state GRAM and NanoGRAM consume  $14.9 \times$  and  $6.8 \times$  more bandwidth, respectively, compared to state-of-the-art interactive RAM-model 2PC [WCS15]. This bandwidth overhead demonstrates the concrete performance penalty resulting from the extra  $\text{poly log log}$  factors.

Last but not least, both NanoGRAM [HKO22, PLS23] and tri-state GRAM [HKO23] assess concrete performance only via cost simulators, which are inadequate for evaluating the actual running time of the garbler and evaluator. A full-fledged implementation remains essential for a comprehensive understanding of practical performance.

In existing garbled RAM constructions [HKO22, PLS23, HKO23], a core building block is a garbled stack, which over time receives an array of  $t$  data elements, each of width  $W$ , marked with a bit indicating whether the element is wanted. The stack then routes all desired elements to the front of the output array, discarding the undesired ones. Prior works showed how to construct such a garbled stack of size  $O(\lambda \cdot W \cdot \log t)$ . Since the garbled stack is repeatedly used in the garbled RAM construction, it becomes a performance bottleneck, both asymptotically and concretely.

**Our novel techniques.** We devise a new garbling technique that reduces the garbled stack size to  $O(\lambda(W + \log t))$ . This improvement not only eliminates the extra  $\text{poly log log}$  factors asymptotically, but also significantly improves the concrete cost of garbled RAM.

To achieve this, our key idea is to augment the tri-state circuit model proposed by Heath et al. [HKO23] with SIMD gates, which can apply the same (routing) operations to the  $W$  bits of a data element. We then devise a new technique, based on the DDH assumption, to garble SIMD gates efficiently. We believe that our SIMD garbling technique can be of independent interest, for

example, in constructing customized garbled data structures and algorithms without relying on the generic garbled RAM transformation.

## 1.4 Additional Related Work

We now review some additional related work.

**Succinct Garbled RAM.** A theoretical line of work on succinct Garbled RAM [LP14, BGL<sup>+</sup>15, CHJV15, KLW15, CCHR16, CH16, CCC<sup>+</sup>16, ACC<sup>+</sup>16, AL18] showed that assuming the existence of indistinguishability obfuscation (iO) [GGH<sup>+</sup>13a, JLS20], we can garble a RAM program such that the size, space requirements, and runtime of the garbled program are the same as those of the input program, up to polylogarithmic factors and a polynomial in the security parameter. While this line of work is theoretically fascinating, it is completely impractical due to the use of iO. Also, the total cost of these schemes (bandwidth + computation) are asymptotically worse than PicoGRAM—in fact, this line of work never even bothered to spell out the “poly” term in the polylogarithmic overhead.

**Oblivious RAM.** A Garbled RAM scheme can be viewed as a non-interactive version of Oblivious RAM [GO96]. Known Garbled RAM [LO13, GHL<sup>+</sup>14, GLO15, LO15, HKO22, PLS23, HKO23] and RAM-model 2PC [GKK<sup>+</sup>12, WCS15, LWN<sup>+</sup>15, Kel20] schemes are also built from an underlying ORAM scheme. It is well known that an ORAM scheme must suffer from a logarithmic slowdown relative to the original program [GO96, LN18]. In the *computationally secure* setting, recent work has shown how to get an ORAM scheme that matches the logarithmic lower bound [PPRY18, AKL<sup>+</sup>23, AKLS23], relying on the existence of pseudorandom functions (PRFs). In comparison, the best known *statistically secure* ORAMs [SDS<sup>+</sup>18, WCS15] are a logarithmic factor worse in performance asymptotically.

Despite this, all known RAM-model 2PC as well as garbled RAM schemes adopt a *statistically secure* ORAM for two reasons: 1) the best known statistically secure constructions [SDS<sup>+</sup>18, WCS15] are simple and enjoy small constants in the big-O; and 2) using a computationally secure scheme would require garbling a PRF, which is concretely inefficient due to the non-blackbox use of cryptography. For these reasons, we use 2PC atop Circuit ORAM [WCS15] as the interactive baseline in our paper.

## 2 Roadmap

### 2.1 Background: Tri-State Circuits and Inefficient Strawman

**From standard Boolean circuits to tri-state circuits.** As mentioned, the main challenge is due to the difficulty of efficiently expressing a memory access in a standard Boolean circuit. An alternative way to view this problem is that the garbler cannot predict in advance which address will be accessed at each time step. Thus, it cannot determine a priori which *label* will encode the memory states or the outcome of memory fetches.

The elegant tri-state GRAM work [HKO23] proposed a solution to this problem. Instead of using standard Boolean circuits as the underlying computation model, it introduces a new computation model called tri-state circuits (TSC). The key differences between a standard Boolean circuit and a TSC are as follows:

1. *Order of evaluation.* In a standard Boolean circuit, we can always evaluate the circuit by populating the wires in some fixed topological order, regardless of the input values. In contrast,

a TSC allows gates to have control signals. Such a gate can be invoked only if its control signal receives a certain input value (e.g., 0). Since the control signals eventually depend on the input values, whether each gate can be invoked and the order in which the gates are invoked depend on the input values.

2. *Subset of active gates under partial input.* As a direct consequence of the above, in a TSC, upon receiving a *partial* input, the subset of gates that can be invoked depends on the input values. In contrast, in a standard Boolean circuit, the subset is determined solely by which input wires are populated, irrespective of their values.

Note that the second difference is relevant even if the RAM program always receives its input all at once. This is because, from the perspective of the garbled gadgets underlying the garbled RAM, inputs may still arrive gradually over time.

**Using a TSC to express Circuit ORAM.** With TSCs, we can encode dynamic memory accesses efficiently with the help of an Oblivious RAM (ORAM) algorithm. It is well-known that every RAM program can be converted to an ORAM with only polylogarithmic blowup in its running time. Specifically, we rely on Circuit ORAM [WCS15]. In Circuit ORAM — ignoring the recursion for now — every memory access translates to accessing  $O(1)$  random paths in a binary tree of size  $O(N)$ , where each path goes from the root to some leaf node<sup>2</sup>. Further, which paths are invoked is computed dynamically at evaluation time.

To gain intuition, it helps to focus on the following technical core of the problem, that is, *routing data along a tree path*. Imagine that in each time step, the root receives some data (denoted `data`) and an address (denoted `addr`) as input, and it needs to pass the data to a leaf node selected by the address. This task can be efficiently expressed as a TSC — imagine that each node in the tree is associated with some routing circuitry, and which nodes are invoked in each time step is determined dynamically. As mentioned, this can be naturally expressed in a TSC by using control wires to signal whether a gate can be invoked.

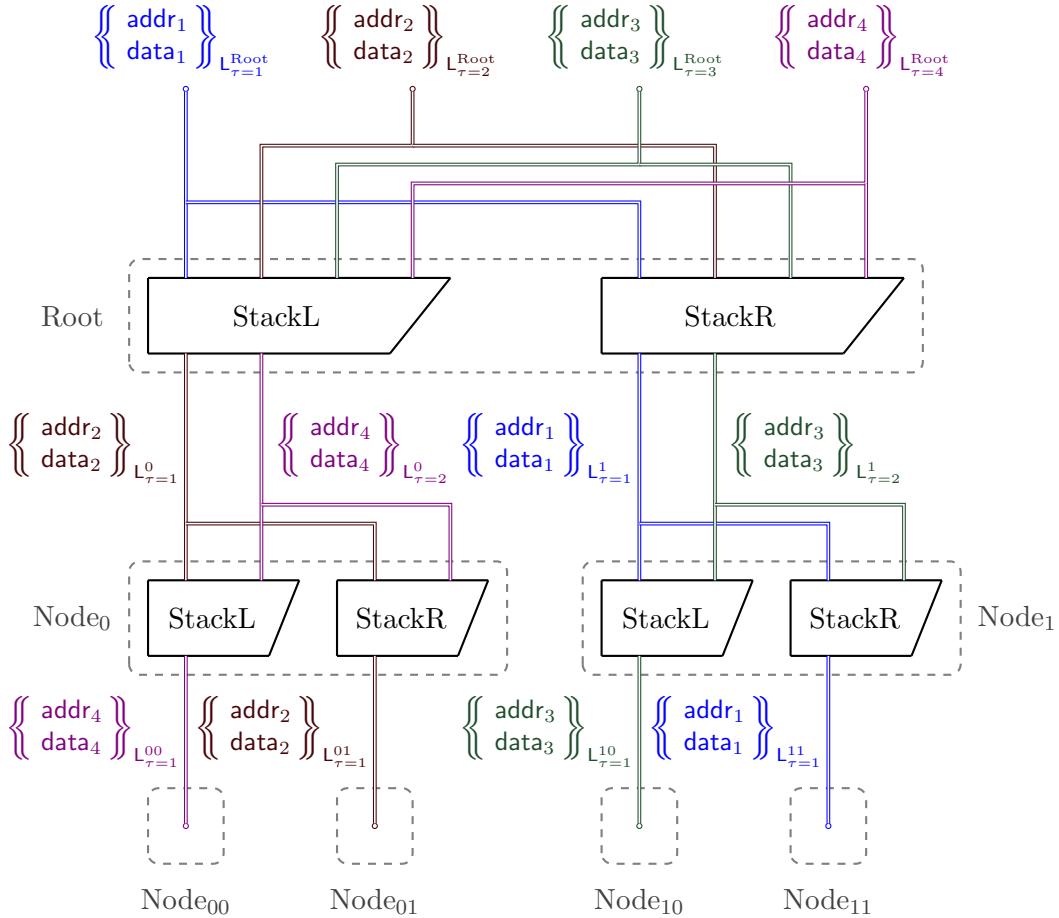

Heath et al. [HKO23] proposed an elegant approach for garbling such a TSC, as shown in Figure 1. Specifically, one can imagine that each non-leaf node  $u$  is associated with two garbled stacks, denoted `StackL` and `StackR`, used for routing to  $u$ 's left and right children, respectively. Below we take `StackL` as an example since `StackR` is symmetric. The stack has  $n_{\max}(u)$  input wires for receiving up to  $n_{\max}(u)$  inputs of the form  $(\text{addr}, \text{data})$  — see Table 3 for the choices of  $n_{\max}(u)$ . Whenever it receives a new input, the stack examines a corresponding bit in the `addr` field: if the bit is 1, no new output wire will be populated; else if the bit is 0, then the next group of  $W = |\text{addr}| + |\text{data}|$  output wires will be populated with the value  $(\text{addr}, \text{data})$ , to be passed to the left child. Further, when the output wires are populated, the tuple  $(\text{addr}, \text{data})$  will be encoded under the label that the left child expects. Specifically, for any node  $v$ , the  $\tau$ -th time it is invoked, it expects the inputs to be encoded using the label  $L_\tau^v$  — earlier works also referred to  $\tau$  as node  $v$ 's *local clock* [PLS23].

For simplicity, we consider the most important special case when  $T = N$ , meaning that the RAM's running time equals its space. Given this case, the other cases  $T < N$  and  $T > N$  can be easily handled using the analysis in Section A.1. In this setting, we know that a stack at the root level (i.e., level 0) will be invoked exactly  $N$  times; a stack at level 1 will be invoked  $N/2$  times in expectation; a stack at level 2 will be invoked  $N/4$  times in expectation; and so on. Finally, a stack at level  $\log(N/B)$  (i.e., the last level of the ORAM tree) will be invoked  $B \in \log N \cdot \omega(1)$  times in expectation for some super-constant function  $\omega(1)$ . Due to the Chernoff bound, it suffices to

---

<sup>2</sup>For best concrete efficiency, the read path is random while the eviction paths should be chosen based on a deterministic reverse lexicographical ordering [WCS15]. However, this detail is not important at this point.

Figure 1: Routing data in a tree using a SIMD tri-state circuit. The notation  $\{\{\text{addr}, \text{data}\}\}_{L_\tau^u}$  means that the tuple  $(\text{addr}, \text{data})$  is encoded under the  $\tau$ -th label associated with node  $u$ . Each non-leaf node  $u$  maintains two garbled stacks, StackL and StackR, for routing data to its children. Each stack looks at a bit in  $\text{addr}$  to decide whether to route  $\text{data}$  to its left or right child, populating the next unconsumed cable of either StackL or StackR. For example,  $(\text{addr}_1, \text{data}_1)$  is eventually routed to the leaf Node10,  $(\text{addr}_2, \text{data}_2)$  is eventually routed to the leaf Node00, and so on.

Table 3: Amortized communication costs from the stacks for routing along a path in a single ORAM tree where  $B = \log N \cdot \omega(1)$ . In the full ORAM, each recursion level will consume  $O(1)$  copies of this routing circuitry, for the read and eviction operations, respectively.

| ORAM Tree                          | Exp.# access | Max# access             | Stack Comm.                       | Bkt Comm.                      |                                |

|------------------------------------|--------------|-------------------------|-----------------------------------|--------------------------------|--------------------------------|

|                                    |              |                         | <i>TSC Stack</i>                  | <i>PicoGRAM Stack</i>          |                                |

|                                    | $N$          | $2N$                    | $O(\lambda W \log 2N)$            | $O(\lambda(W + \log 2N))$      | $O(\lambda W \log N)\omega(1)$ |

|                                    | $N/2$        | $N$                     | $O(\lambda W \log N)$             | $O(\lambda(W + \log N))$       | $O(\lambda W)$                 |

| $\vdots \quad \vdots \quad \vdots$ | $\vdots$     | $\vdots$                | $\vdots$                          | $\vdots$                       | $\vdots$                       |

|                                    | $2B$         | $4B$                    | $O(\lambda W \log 4B)$            | $O(\lambda(W + \log 4B))$      | $O(\lambda W)$                 |

|                                    | $B$          | $2B$                    | $O(\lambda W \log 2B)$            | $O(\lambda(W + \log 2B))$      | $O(\lambda WB)$                |

| <b>Total</b>                       |              | $O(\lambda W \log^2 N)$ | $O(\lambda(W \log N + \log^2 N))$ | $O(\lambda W \log N)\omega(1)$ |                                |

provision each level with a maximum number of invocations that is twice its expectation. Since we stop the tree at level  $\log(N/B)$  with a super-logarithmic number of invocations in expectation, it is not hard to see that the actual number of invocations does not exceed the provisioned maximum except with negligible probability.

**Inefficiency of tri-state GRAM.** The cost of tri-state GRAM [HKO23] is dominated by garbling the routing stacks in the ORAM tree. Specifically, tri-state GRAM showed how to garble a stack achieving the following efficiency:

**Fact 2.1** (Inefficient garbled stack of tri-state GRAM [HKO23]). Garbling a stack provisioned for  $t$  accesses results in a garbled circuit of size  $O(\lambda \cdot W \cdot \log t)$  amortized.

As shown in Table 3, plugging in Fact 2.1 and summing over all garbled stacks in the entire ORAM tree, the amortized communication cost comes to  $O(\lambda \cdot W \cdot \log^2 N)$ .

To complete the analysis, we must also account for the fact that a full ORAM scheme has  $O(\log N)$  recursively constructed ORAM trees: one data tree that adopts a word size of  $W = |\text{data}| + |\text{addr}|$ , and multiple metadata trees. The  $\ell$ -th metadata tree has  $2^{O(\ell)}$  leaves and a word size of  $O(\ell)$ . Therefore, the amortized cost for garbling the stacks across all recursion levels is

$$O(\lambda \cdot W \cdot \log^2 N) + \sum_{\ell=1}^{O(\log N)} O(\lambda \cdot \ell \cdot \ell^2) = O(\lambda \cdot (W + \log^2 N) \cdot \log^2 N)$$

**Remark 2.2.** Table 3 shows an asymptotically slower variant of tri-state GRAM [HKO23]. To achieve their asymptotics as claimed in Table 1, they need an additional “reset” trick similar to Nanogram [PLS23]. Specifically, instead of provisioning for  $2N, N, N/2, \dots$  stack accesses at each level of the ORAM tree, they create stacks provisioned for polylogarithmically many accesses at all levels, but each level must initialize a new garbled stack every polylogarithmically many accesses. Using the reset trick, each single ORAM tree in tri-state GRAM incurs  $O(\lambda \cdot W \cdot \log N \cdot \log \log N)$  cost instead of  $O(\lambda \cdot W \cdot \log^2 N)$  per access. Therefore, the total garbled stack cost over all recursion levels is  $O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot \log \log N)$ . However, this reset trick does not further benefit PicoGRAM, as we already get significant savings by reducing the multiplicative overhead to additive — see Section 2.2 for more details.

## 2.2 Our Blueprint: Extending Tri-State Circuits with SIMD Gates

**From multiplicative to additive.** Tri-State GRAM’s garbled stack incurs  $O(\lambda \cdot W \cdot \log t)$  cost for supporting  $t$  accesses, where the  $W$  and the  $\log t$  factors accumulate *multiplicatively*. We devise new techniques leading to a new garbled stack whose cost is only  $O(\lambda \cdot (W + \log t))$ , where the  $W$  and the  $\log t$  factors are now *additive*.

Assuming we can achieve this, then, by Table 3 and the analysis shown in Section 2.1, we can reduce the total garbled stack cost to  $O(\lambda \cdot (W \cdot \log N + \log^3 N))$ , summing over all recursion levels of the ORAM. At this point, the garbled stack cost is no longer dominating. Instead, PicoGRAM’s cost is dominated by the data-read circuitry associated with the nodes in the ORAM tree. Specifically, besides the routing circuitry (i.e., the stacks), each node in the ORAM tree also has additional garbled circuitry that implements a Garbled Bucket, for reading and writing the memory words stored in this node. In PicoGRAM, every node has a constant-sized Garbled Bucket, except the root and the leaf levels, which have super-logarithmically sized Garbled Buckets. Moreover, the circuit size for each access in Circuit ORAM is linear in the bucket size and the word width, assuming a word-RAM model where the word width  $W \in \Omega(\log N)$ . In Table 3, we also account for the cost of the Garbled Buckets. For a single ORAM tree, this cost comes to  $O(\lambda W \log N) \omega(1)$ . Since there are logarithmically many trees, one with word size  $W$ , and the rest with word size  $W' = O(\log N)$ , the total cost across all recursion levels is

$$O(\lambda \cdot (W \cdot \log N + \log^3 N) \cdot \omega(1))$$

With some additional algorithmic tricks, we can further reduce the above expression to  $O(\lambda \cdot (W \cdot \log N \cdot \omega(1) + \log^3 N))$ . We describe the details in Section A.2.

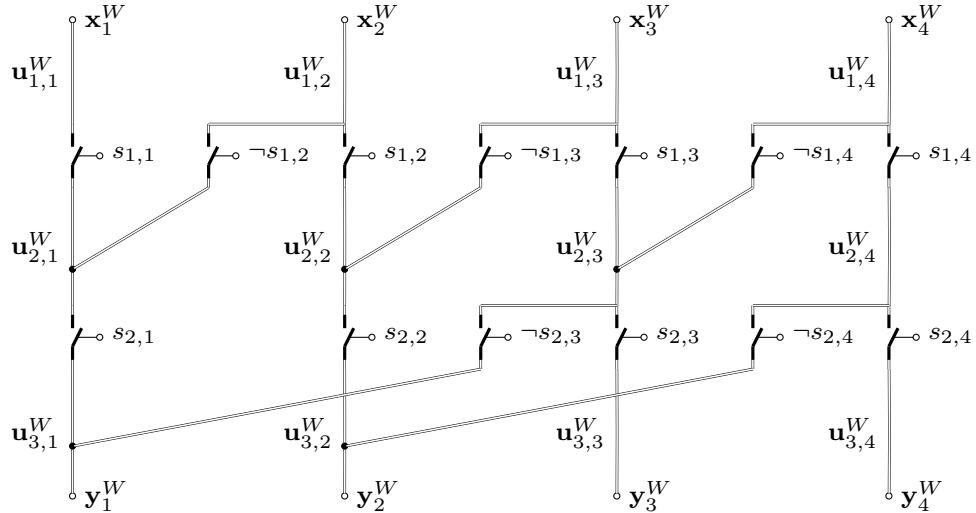

**Introducing SIMD gates.** We observe that the dominant cost of the garbled stack comes from the routing circuitry that routes all  $W$  bits of the payload in a synchronized fashion. We refer to such operations as SIMD (Single Instruction Multiple Data). Our key idea is to extend the original tri-state circuit—designed to operate on individual bits—with new SIMD gates that process groups of  $W$  bits in parallel. Furthermore, leveraging the DDH assumption, we propose an efficient method for garbling these SIMD gates.

Henceforth, we use the term *cable* to denote a group of  $W$  wires, where each wire carries a single bit. A wire that is not part of a cable is sometimes called an *independent wire*. A wire that is part of a cable is called a *subwire*. We use boldface notation such as  $\mathbf{x}^W$  to denote a cable, whose  $i$ -th wire is denoted as  $x_i$ . Our enriched circuit model consists of the following types of gates:

- **Boolean gate** ( $z \leftarrow f(x, y)$ ): A Boolean gate takes two independent input wires  $x$  and  $y$  and outputs an independent wire  $z$ . It defines an evaluation rule  $z \leftarrow f(x, y)$ , where  $f$  is a Boolean function. The Boolean gate can be evaluated only when both  $x$  and  $y$  are set.

- **Group gate**  $y_i \xleftarrow{\text{grp}} x$ : The Group gate converts an independent wire  $x$  into a subwire  $y_i$  of a cable. It defines the evaluation rule  $y_i \leftarrow x$ .

- **Ungroup gate**  $y \xleftarrow{\text{ungrp}} x_i$ : The Ungroup gate converts a subwire  $x_i$  back to an independent wire  $y$ . It defines the evaluation rule  $y \leftarrow x_i$ .

- **Switch gate** ( $\mathbf{x}^W \xrightarrow{c} \mathbf{y}^W$ ): A Switch gate connects two cables  $\mathbf{x}^W$  and  $\mathbf{y}^W$  of equal width and an independent control wire  $c$  that determines whether the gate is active. If  $c = 0$ , the gate enforces equality between every pair of subwires  $x_i$  and  $y_i$ . In other words, the Switch gate defines  $2W$  evaluation rules:  $c = 0 \Rightarrow y_i \leftarrow x_i$  and  $c = 0 \Rightarrow x_i \leftarrow y_i$  for  $i \in [W]$ . The gate may be evaluated partially even if some subwires are not set. Conceptually, our Switch gate has

the same functionality as a collection of  $W$  Buffer gates sharing the same control wire in prior works [HKO23, Hea24]. Moreover, we remove the Join gate from prior works [HKO23, Hea24] for simplicity, and instead allow a subwire to be set by multiple gates.

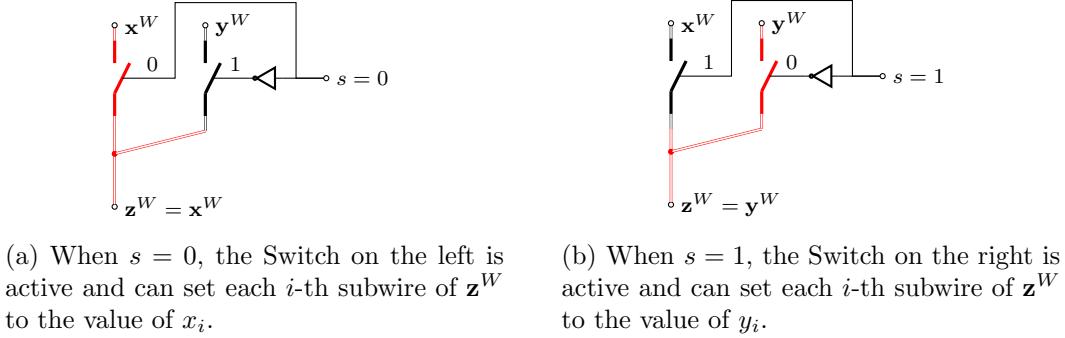

**Operational semantics.** Unlike the standard Boolean circuit model, the SIMD tri-state circuit allows a subwire to be set by multiple gates. In Figure 2, we show an example that employs this behavior to achieve indirect addressing with a 1-bit address space. To avoid non-deterministic behavior during evaluation, we say a SIMD tri-state circuit is **well-formed** only if every wire in the circuit can be set to a unique value, regardless of the order of evaluation. For well-formed SIMD tri-state circuits, we further define a stronger property called **strictly well-formed**, which enforces a partial ordering on the wires. We formally describe our computational model in Section 3.

Figure 2: A  $1 \times 2$  multiplexer implemented with SIMD tri-state gates. Since the two Switches can never be active at the same time, the value of each  $z_i$  is uniquely determined when the inputs  $\mathbf{x}^W$ ,  $\mathbf{y}^W$ , and  $s$  are fixed. Compared to Boolean circuit, the SIMD tri-state circuit allows  $z_i$  to be set in an eager manner. For instance, when  $s = 0$ , the value of  $z_i$  can be set to  $x_i$  without waiting for the value of  $y_i$  to be known.

### 2.3 Garbling SIMD Tri-State Circuits

In this work, we propose two garbling schemes for the SIMD tri-state circuit, both assuming DDH. The first scheme achieves the asymptotic efficiency of GRAM and is proven secure in the plain model, while the second scheme offers better concrete efficiency at the cost of relying on the Random Oracle (RO) model. Additionally, the first scheme requires the SIMD tri-state circuit to be strictly well-formed, whereas the second scheme only requires well-formedness, which further helps to reduce the concrete circuit size of GRAM.

We focus on introducing the first scheme in the main body and defer the second scheme to Section C.

**Background: Yao’s Garbling for Boolean Gates [Yao86].** We use the standard Yao’s garbling scheme [Yao86] to garble the Boolean gates in our SIMD tri-state circuit. For every independent wire  $x$ , the garbler samples two random labels  $L_{x=0}$  and  $L_{x=1}$  from  $\{0, 1\}^\lambda$ , where  $\lambda$  is the security parameter. Assume that we have an encryption scheme that reveals whether the decryption key is correct with high probability. To garble a Boolean gate  $z \leftarrow f(x, y)$ , the garbler encrypts the output label  $L_{z=f(a,b)}$  with the labels of the input wires  $L_{x=a}$  and  $L_{y=b}$  for every  $a, b \in \{0, 1\}$ , and randomly shuffles the ciphertexts before sending them to the evaluator. The evaluator, in turn, only learns the label corresponding to the runtime value of each wire, called the active label. Initially, the evaluator only holds the active labels of the circuit’s input wires. If the evaluator

learns the active labels of both  $x$  and  $y$  in the Boolean gate, they can decrypt the corresponding ciphertext and obtain the active label of  $z$ .

**Encoding of subwires.** Next, we propose a novel technique to encode the subwires in the SIMD tri-state circuit, enabling efficient garbling of Switch gates.

Conceptually, our garbling scheme encodes all cables in the circuit with two “orthogonal” sets of keys. The first set of keys is global for all cables but unique for each subwire offset. The second set of keys is local to each cable but shared among all subwires of that cable.

Let  $\mathbb{G}_q$  be a prime-order group where the DDH assumption holds and  $g$  be a generator of  $\mathbb{G}_q$ . The garbler samples  $2 \cdot W_{\max}$  global keys  $\Gamma_{i,b}$  from  $\mathbb{Z}_q^*$ , where  $i \in [W_{\max}]$ ,  $b \in \{0, 1\}$ , and  $W_{\max}$  is the maximum width of any cable in the circuit. For each  $W$ -bit cable  $\mathbf{x}^W$ , the garbler samples a local key  $\mathbf{K}_x$  from  $\mathbb{Z}_q^*$ .

We define the labels of the  $i$ -th subwire as

$$\mathsf{L}_{x_i=0} = g^{\mathbf{K}_x \cdot \Gamma_{i,0}}, \quad \mathsf{L}_{x_i=1} = g^{\mathbf{K}_x \cdot \Gamma_{i,1}}.$$

As a sanity check, the evaluator should not be able to infer whether a subwire carries 0 or 1 from the labels. Consider  $t$  cables each of width  $W$ . Let  $k_\tau$  be the local key of the  $\tau$ -th cable. Then, the subwire labels are a subset of the following  $t \times 2W$  matrix over  $\mathbb{G}_q$ :

$$M = \begin{pmatrix} g^{k_1 \cdot \Gamma_{1,0}} & \dots & g^{k_1 \cdot \Gamma_{W,0}} & g^{k_1 \cdot \Gamma_{1,1}} & \dots & g^{k_1 \cdot \Gamma_{W,1}} \\ \vdots & \ddots & \vdots & \vdots & & \vdots \\ g^{k_t \cdot \Gamma_{1,0}} & \dots & g^{k_t \cdot \Gamma_{W,0}} & g^{k_t \cdot \Gamma_{1,1}} & \dots & g^{k_t \cdot \Gamma_{W,1}} \end{pmatrix}$$

It has been shown in the work of the BHHO cryptosystem [BHHO08] that  $M$  is computationally indistinguishable from a random matrix. Nonetheless, in Section 4, we prove more directly that all the subwire labels can be replaced one by one with random group elements.

**Garbling Switch gates.** To garble a Switch gate  $\mathbf{x}^W \xrightarrow{c} \mathbf{y}^W$ , the garbler encrypts the ratio of the two cables’ local keys with the zero-label of the control wire  $c$ . Specifically, the garbler sends  $\mathsf{Enc}_{\mathsf{L}_{c=0}}(\mathbf{K}_x^{-1} \cdot \mathbf{K}_y)$ .

If the evaluator learns  $\mathsf{L}_{c=0}$ , the zero-label of the control wire, they can decrypt the ciphertext and obtain  $\mathbf{K}_x^{-1} \cdot \mathbf{K}_y$ . If the evaluator also learns the active label of a subwire  $x_i$ , they can compute the active label of the corresponding subwire  $y_i$  as follows:

$$\mathsf{L}_{y_i=b} = g^{\mathbf{K}_y \cdot \Gamma_{i,b}} = (\mathsf{L}_{x_i=b})^{\mathbf{K}_x^{-1} \cdot \mathbf{K}_y}.$$

Similarly, the evaluator can compute the modular inverse of  $\mathbf{K}_x^{-1} \cdot \mathbf{K}_y$  and obtain the active label of  $x_i$  from that of  $y_i$ .

These properties match our evaluation rule for the Switch gate: the evaluator can propagate values between each pair of subwires if and only if the control wire is 0.

The garbled Switch gate reveals the value of the control wire  $c$ , as the evaluator learns whether the active label of the control wire is the correct decryption key. Previous works [HKO23, Hea24] have shown that such leakage does not affect the security of the final Garbled RAM construction, due to the randomness of the ORAM algorithms.

We set the prime order  $q$  to be an  $O(\lambda)$ -bit prime. The communication cost of our garbled Switch gate is  $O(\lambda)$  bits, independent of the width  $W$  of the cables. This is a significant improvement over previous works [HKO23, Hea24], which require  $O(W \cdot \lambda)$  bits of communication to garble an equivalent Switch gate.

**Garbling Group and Ungroup gates.** Finally, we garble Group and Ungroup gates using Yao’s garbling [Yao86], similar to Boolean gates. Since each gate has only one input wire, the garbler sends two ciphertexts  $\text{Enc}_{L_{x_{\text{in}}=0}}(L_{x_{\text{out}}=0})$  and  $\text{Enc}_{L_{x_{\text{in}}=1}}(L_{x_{\text{out}}=1})$  in random order, where  $x_{\text{in}}$  is the input wire and  $x_{\text{out}}$  is the output wire. The communication cost of garbling a Group or Ungroup gate is  $O(\lambda)$  bits.

## 2.4 Efficient Garbled Stack

**Applying SIMD gates to the stack.** Recall that our goal is to eliminate the multiplicative factor  $W$  from the communication cost of garbled stack constructions in prior work [HKO23]. To achieve this, we store data words as cables within the stack and route them using our new Switch gates. Although we need to convert independent wires into cables when pushing data into the stack, and convert them back when popping data, the number of Group and Ungroup gates required depends only on the number of input and output wires, not on the size of the stack circuit. As a result, the total cost of the garbled stack is  $O(\lambda \cdot (W + \log t))$  bits, where  $t$  is the maximum number of accesses to the stack and  $W$  is the word width.

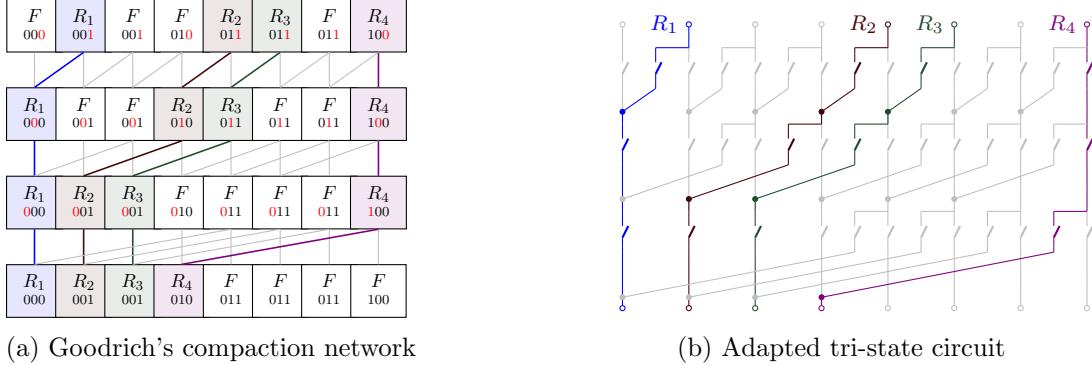

**Optimizing stack circuitry.** While our SIMD gates reduce the asymptotic cost of GRAM, we further optimize the stack’s circuitry to improve PicoGRAM’s concrete performance. We observe that it suffices to construct the garbled stack based on an oblivious stable compaction algorithm [Goo11], which is much simpler and more efficient than the oblivious stack data structure [ZE13] used in previous works [HKO22, PLS23, WCS15]. To adapt the original compaction algorithm [Goo11] into a SIMD tri-state circuit, we devised a new method to compute the routing plan, ensuring that the GRAM is strictly well-formed. This optimization alone reduces the communication cost of the garbled stack by a factor of  $4.1\times$  for  $N = 2^{16}$  and word width  $W = 64$ , even without using SIMD gates. Combined with the SIMD garbling technique, we achieve a total of  $24\times$  savings for the stack at  $N = 2^{16}$ , and  $29\times$  at  $N = 2^{20}$ .

## 3 Computational Model: SIMD Tri-State Circuits

In this section, we formally define SIMD tri-state circuits, which extend the original tri-state circuit model [HKO23] with gates that support SIMD (Single Instruction, Multiple Data) operations.

### 3.1 Definitions

**Wires and cables.** As in the original tri-state circuit model [HKO23], we treat a circuit as a finite state machine, where each wire holds a state of 0, 1, or  $\mathcal{Z}$ , meaning the wire has not yet received any signal.

In addition to wires that each carry a single bit, we introduce the concept of a **cable**, representing a group of  $W$  wires that act in a SIMD fashion. A wire is **set** if its state is not  $\mathcal{Z}$ . A wire can belong to at most one cable. Wires that do not belong to any cable are called *independent wires*.

We denote an independent wire with a lowercase letter, e.g.,  $x$ , and a cable of  $W$  wires with a boldfaced letter and a superscript, e.g.,  $\mathbf{x}^W$ , where  $W$  is the **width** of the cable. The  $i$ -th wire of  $\mathbf{x}^W$  is written as  $x_i$ , where  $i \in [W]$  is called the **offset** of the subwire.

Each wire or cable has a type: *input*, *output*, or *internal*. We may assume all cables are of type *internal*, i.e., all input and output wires are independent wires. This is because we can always introduce additional Group and Ungroup gates (defined below) to convert an independent wire to a subwire of a cable and vice versa, without increasing the circuit size asymptotically.

**Evaluation rules.** An *evaluation rule* specifies how to set a wire. We represent an evaluation rule as  $P \Rightarrow x \leftarrow S$ , where  $P$  is a precondition and  $S$  is an expression that computes the state of wire  $x$ . To apply the evaluation rule,  $S$  must evaluate to either 0 or 1, and  $P$  must be true. If  $P$  is trivial, we write the rule simply as  $x \leftarrow S$ . The evaluation rule is allowed to change the state of a wire.

**Gates.** Each gate defines a set of evaluation rules applied to wires or cables. Our SIMD tri-state circuit comprises the following types of gates:

- **Boolean** ( $z \leftarrow f(x, y)$ ): A Boolean gate sets an independent output wire  $z$  based on a public Boolean function  $f : \{0, 1\} \times \{0, 1\} \mapsto \{0, 1\}$  and the values of two independent input wires  $x$  and  $y$ .

- **Group** ( $y_i \xleftarrow{\text{grp}} x$ ): A Group gate sets a subwire of a cable  $\mathbf{y}^W$  to the value of an independent wire  $x$ .

- **Ungroup** ( $y \xleftarrow{\text{ungrp}} x_i$ ): An Ungroup gate sets an independent output wire  $y$  to the value of a subwire of a cable  $\mathbf{x}^W$ .

- **Switch** ( $\mathbf{x}^W \xrightarrow{c} \mathbf{y}^W$ ): A Switch gate connects two cables  $\mathbf{x}^W$  and  $\mathbf{y}^W$  of equal width and an independent wire  $c$ , called the **control wire**. For each  $i \in [W]$ , when  $c = 0$ , the gate is **active** and can either set the  $i$ -th subwire  $x_i$  to the value of  $y_i$  or set  $y_i$  to the value of  $x_i$ , depending on which wire is set first. When  $c = 1$ , the gate is **inactive**, meaning it cannot set any wire.

**Number of wire sources.** As in the classic circuit model, we require each independent wire to be either an input wire of the circuit or the output wire of a single gate. However, we do not apply this restriction to cables, since the subwires of cables are meant to be set by one of multiple gates, depending on the runtime state of the circuit. Also, we do not bound the circuit’s fan-out: each wire can be input to any number of gates.

## 3.2 Operational Semantics

**Evaluating a SIMD tri-state circuit.** Unlike traditional Boolean circuits, in a (SIMD) tri-state circuit, both the order in which gates are evaluated and the directions of evaluation may vary based on the input values. Thanks to this new semantics, we can express RAM computations efficiently in a (SIMD) tri-state circuit [HKO23].

The *state* of a SIMD tri-state circuit  $\mathcal{C}$  refers to the combined states of all wires in  $\mathcal{C}$ . Evaluating the circuit  $\mathcal{C}$  can thus be viewed as a sequence of state transitions.

- *Initial state.* Initially, every input wire receives a bit, and all other wires have the state  $\mathcal{Z}$ .

- *Evaluation.* At each time step, look for a gate with an evaluation rule that can be invoked, and execute the evaluation rule to populate a wire.

- *Output.* Eventually, output the values on the output wires.

The above evaluation algorithm exhibits non-determinism: a wire may be set by the evaluation rules of multiple gates. If, under some evaluation state, multiple rules (associated with gates) are invocable, the evaluator may break ties arbitrarily and select one of them. Despite this non-deterministic behavior, we want a *well-formed* SIMD tri-state circuit to satisfy the following natural property: given any valid input  $\text{inp}$ , every wire can be set, and moreover, that value must be unique.

Table 4: Gate set of our SIMD tri-state circuit.

| Type    | Notation                                    | Evaluation Rules                                                                 |

|---------|---------------------------------------------|----------------------------------------------------------------------------------|

| Boolean | $z \leftarrow f(x, y)$                      | $z \leftarrow f(x, y)$                                                           |

| Group   | $y_i \xleftarrow{\text{grp}} x$             | $y_i \leftarrow x$                                                               |

| Ungroup | $y \xleftarrow{\text{ungrp}} x_i$           | $y \leftarrow x_i$                                                               |

| Switch  | $\mathbf{x}^W \xrightarrow{c} \mathbf{y}^W$ | $c = 0 \Rightarrow y_i \leftarrow x_i$<br>$c = 1 \Rightarrow x_i \leftarrow y_i$ |

More specifically, under any fixed input  $\text{inp}$ : 1) a wire should not take on two different values across two evaluations; and 2) a wire should not acquire a value  $b \in \{0, 1\}$  and then later switch to  $1 - b$  in the same evaluation. We introduce a sufficient condition, called *dynamic well-formedness*, to formalize this notion.

Henceforth, we say that a state  $\mathcal{S}$  of  $\mathcal{C}$  is **total** if and only if no wire holds  $\mathcal{Z}$ . A state  $\mathcal{S}$  of  $\mathcal{C}$  is **reachable** from another state  $\mathcal{S}'$  of  $\mathcal{C}$  if and only if  $\mathcal{S}$  can be obtained from  $\mathcal{S}'$  by applying a sequence of evaluation rules defined by the gates in  $\mathcal{C}$ .

We often use  $\text{inp}$  to denote the input or the input wires to  $\mathcal{C}$  and  $|\text{inp}|$  to represent the input length.

**Definition 3.1** (Well-formed). A SIMD tri-state circuit  $\mathcal{C}$  is **well-formed** if and only if for any input  $\text{inp} \in \{0, 1\}^{|\text{inp}|}$ , there is a unique total state  $\mathcal{S}$  of  $\mathcal{C}$  reachable from the initial state determined by  $\text{inp}$ .

**Efficient evaluation.** As a direct implication of Definition 3.1, a well-formed SIMD tri-state circuit  $\mathcal{C}$  can be evaluated *efficiently*. Specifically, in the evaluation algorithm above, at each time step, we always look for a rule that populates a previously unset wire. This way, the evaluation algorithm completes in  $|\mathcal{C}|$  steps, where  $|\mathcal{C}|$  denotes the size of the circuit. We prove this formally in Lemma 3.2. Note that the evaluation rules in Table 4 also specify a **topological ordering for evaluation** that governs the order in which gates are invoked for a fixed input.

**Lemma 3.2.** *Let  $\mathcal{C}$  be a well-formed SIMD tri-state circuit. Then, the above evaluation algorithm terminates within  $O(|\mathcal{C}|)$  state transitions on any  $\text{inp} \in \{0, 1\}^{|\text{inp}|}$ , and reaches a total state at the end, as long as in every time step, we always invoke a rule that populates an unset wire.*

*Proof.* First, we show that during the evaluation, every wire must be set to the same value as in the unique total state  $\mathcal{S}$  reachable from the initial state given by  $\text{inp}$ . Suppose that a wire  $x$  is the first wire set to a different value than in  $\mathcal{S}$ , and let  $\mathcal{R}$  be the evaluation rule applied. Then all the rest of the wires used in  $\mathcal{R}$  must have the same value as in  $\mathcal{S}$  when the rule is applied, so  $\mathcal{R}$  can also be applied upon  $\mathcal{S}$  and transition it to another total state where  $x$  is set differently. This contradicts the uniqueness of total state.

Now, suppose that the evaluation algorithm reaches a state  $\mathcal{S}'$  which is not total but no wire can be further set. Consider a state transition to the total state  $\mathcal{S}$ , and let  $y$  be the first wire set during the transition such that  $y$  is not set in  $\mathcal{S}'$ . Then the evaluation rule applied to set  $y$  must be applicable to  $\mathcal{S}'$ , since all the other wires used in the rule are set in  $\mathcal{S}'$  and have the same value as in  $\mathcal{S}$ . This contradicts the assumption that no wire can be further set in  $\mathcal{S}'$ . Therefore, the evaluation must terminate within  $O(|\mathcal{C}|)$  state transitions.  $\square$

**Incremental evaluation of a tri-state circuit.** If a SIMD tri-state circuit is well-formed, then it is insensitive to the order in which the evaluation rules are invoked. A direct implication is

that the circuit can be evaluated incrementally, accommodating inputs that arrive gradually rather than all at once. This is important for defining the garbled gadgets underlying our Garbled RAM scheme. For example, for the core building block **stack**, inputs do not arrive all at once. The evaluator must eagerly and incrementally evaluate the stack over time as more input bits become available. In fact, when the stack is integrated into a larger tri-state circuit (e.g., our Garbled RAM), subsequent input bits to the stack can only be set once part of the output bits have been evaluated.

In Section C, we propose a garbling scheme for well-formed SIMD tri-state circuits, which is secure under the random-oracle model.

**Strict well-formedness.** To prove the security of the garbling scheme in the plain model, we require the circuit to satisfy a stronger property called strict well-formedness, which imposes additional restrictions on the order in which wires can be set. First, we define the notion of dependency between wires.

**Definition 3.3** (Dependency). Let  $\mathcal{S}$  be the total state of a well-formed SIMD tri-state circuit  $\mathcal{C}$ . We say a wire  $y$  in  $\mathcal{C}$  **depends on** a wire  $x$  (or  $x$  is a **dependency** of  $y$ ) with respect to  $\mathcal{S}$  if any of the following conditions holds:

- $y$  is the output wire of a Boolean, Group, or Ungroup gate with input wire  $x$ .

- $y$  is a subwire connected to a Switch gate whose control wire is  $x$ .

- $y$  is a subwire connected to an **active** Switch gate under the state  $\mathcal{S}$ , and  $z$  depends on  $x$ , where  $z$  is the subwire with the same offset in the other cable connected to the Switch gate.

- $y$  depends on another wire  $z$ , and  $z$  depends on  $x$ .

The dependency relationship defines the order in which we replace garbled gates with their idealized counterparts when proving security through hybrid arguments. Now, we define the notion of strict well-formedness.

**Definition 3.4** (Strictly Well-formed). A well-formed SIMD tri-state circuit  $\mathcal{C}$  is **strictly well-formed** if for any input  $\text{inp} \in \{0, 1\}^{|\text{inp}|}$ , there is an ordering to set all the wires in  $\mathcal{C}$  such that every wire is set after all its dependencies with respect to the unique total state determined by  $\text{inp}$ .

For a general (SIMD) tri-state circuit, there may not be an efficient algorithm to check well-formedness or strict well-formedness. However, for all circuits we construct in this paper, we can prove that they are strictly well-formed.

## 4 Garbling SIMD Tri-State Circuits

### 4.1 Definitions

**Definition 4.1** (Garbling scheme). A garbling scheme, defined for some computation models (e.g., SIMD tri-state circuit, RAM), consists of a tuple of possibly randomized algorithms:

- $\text{sk} \leftarrow \text{Gen}(1^\lambda, \text{params})$ : upon receiving the security parameter  $1^\lambda$  and parameters **params** specific to the computation model of concern, output a secret key  $\text{sk}$ .

- $\widetilde{\text{inp}} \leftarrow \text{Encode}(\text{sk}, \text{inp})$ : upon receiving the secret key  $\text{sk}$  and input  $\text{inp}$ , output a garbled version of the input string denoted  $\widetilde{\text{inp}}$ .

- $\tilde{\mathcal{C}} \leftarrow \text{Garble}(\text{sk}, \mathcal{C})$ : upon receiving  $\text{sk}$  and a deterministic program  $\mathcal{C}$  under the computation model of concern, output a garbled version of the program denoted  $\tilde{\mathcal{C}}$ .

- $\text{out} \leftarrow \text{Eval}(\tilde{\mathcal{C}}, \tilde{\text{inp}})$ : upon receiving the garbled program  $\tilde{\mathcal{C}}$  and garbled input  $\tilde{\text{inp}}$ , outputs the evaluation outcome  $\text{out}$ .

Later, for a SIMD tri-state circuit, we only need to include the input length  $|\text{inp}|$  in  $\text{params}$ ; for a RAM, we include its maximum space requirement  $N$  and maximum runtime  $T$  in  $\text{params}$ .

**Correctness.** A garbling scheme  $(\text{Gen}, \text{Encode}, \text{Garble}, \text{Eval})$  is **correct** if for polynomial-time program  $\mathcal{C}$  with parameters  $\text{params}$ , there exists a negligible function  $\text{negl}(\cdot)$ , such that for all  $\lambda$ , for any input  $\text{inp}$ , except with  $\text{negl}(\cdot)$  probability, the following holds: let  $\text{sk} \leftarrow \text{Gen}(1^\lambda, \text{params})$ ,  $\tilde{\text{inp}} \leftarrow \text{Encode}(\text{sk}, \text{inp})$ ,  $\tilde{\mathcal{C}} \leftarrow \text{Garble}(\text{sk}, \mathcal{C})$ , then, it must be that  $\text{Eval}(\tilde{\mathcal{C}}, \tilde{\text{inp}}) = \mathcal{C}(\text{inp})$  where  $\mathcal{C}(\text{inp})$  denotes the outcome of executing the program  $\mathcal{C}$  on the input  $\text{inp}$  in cleartext.

**Security.** Since we assume a semi-honest setup and a deterministic program  $\mathcal{C}$ , the security definition only requires simulating the evaluator's view given the circuit's output values and the output of a leakage function  $\text{leak}$ .

**Definition 4.2** (Security of garbling scheme). A garbling scheme  $(\text{Gen}, \text{Encode}, \text{Garble}, \text{Eval})$  is **secure** with respect to some (deterministic) leakage function  $\text{leak}$ , if and only if there exists a probabilistic polynomial-time algorithm  $\text{Sim}$  such that for any program  $\mathcal{C}$  with parameters  $\text{params}$ , for any  $\text{inp}$ , the following experiments are computationally indistinguishable:

- **Real:** Run  $\text{sk} \leftarrow \text{Gen}(1^\lambda, \text{params})$ ,  $\tilde{\text{inp}} \leftarrow \text{Encode}(\text{sk}, \text{inp})$ ,  $\tilde{\mathcal{C}} \leftarrow \text{Garble}(\text{sk}, \mathcal{C})$ , and output  $(\tilde{\mathcal{C}}, \tilde{\text{inp}})$ .

- **Ideal:** Output  $\text{Sim}(1^\lambda, \mathcal{C}, \text{leak}(\mathcal{C}, \text{inp}), \mathcal{C}(\text{inp}))$ .

## 4.2 Our Construction from DDH

**Labels.** Similar to Yao's garbled circuit [Yao86], we assign two labels to each wire in a SIMD tri-state circuit, corresponding to the bits 0 and 1, respectively. Henceforth, we use the notation  $\text{L}_{x=b}$  to represent the label for the value  $b \in \{0, 1\}$  on the wire  $x$ .

We sometimes overload the notation  $x$  to also mean the value the wire  $x$  carries; in such cases, we use the shorthand  $\text{L}_x$  for the label of wire  $x$  when it carries the value  $x$ .

**Labels of an independent wire.** The garbler samples two labels from  $\{0, 1\}^\lambda$  for each independent wire, as in Yao's garbling scheme [Yao86].

**Labels of a cable.** We devise a new technique for computing labels of a cable. Let  $\mathbb{G}_q$  be a public prime-order group of order  $q$  where DDH is assumed to hold and  $g$  be a generator. Let  $W_{\max}$  be the maximum width of any cable in the system. The garbler draws  $2W_{\max}$  global keys  $\Gamma_{1,0}, \Gamma_{1,1}, \Gamma_{2,0}, \Gamma_{2,1}, \dots, \Gamma_{W_{\max},0}, \Gamma_{W_{\max},1}$  from  $\mathbb{Z}_q^*$  and hides them from the evaluator.

For each cable  $\mathbf{x}^W$ , the garbler also samples a secret cable key  $\mathbf{K}_x \in \mathbb{Z}_q^*$ . Then the labels of the  $i$ -th wire  $x_i$  of the cable are defined as

$$\text{L}_{x_i=b} = g^{\mathbf{K}_x \cdot \Gamma_{i,b}}$$

**Symmetric-key Encryption Scheme from DDH.** Our garbling scheme assumes the existence of a symmetric-key encryption scheme  $\Pi = (\text{Enc}, \text{Dec})$  that is IND-CPA secure under the DDH assumption and the ciphertext's length is  $O(|m| + \lambda)$  where  $|m|$  is the length of the plaintext and

$\text{Gen}(1^\lambda, |\text{inp}|)$ :

- Sample labels  $\mathsf{L}_{x=b} \xleftarrow{\$} \{0,1\}^\lambda$  for each input wire  $x$  and  $b \in \{0,1\}$ .

- Select a prime-order DDH group  $\mathbb{G}_q$  with security parameter  $\lambda$ , and a generator  $g$  of the group.

- Return  $\text{sk} = (\mathsf{L}, \mathbb{G}_q, g)$ .

$\text{Encode}(\text{sk} = (\mathsf{L}, \text{--}, \text{--}), \text{inp})$ :

- Return  $\widetilde{\text{inp}}$  where  $\widetilde{\text{inp}}[i] \leftarrow \mathsf{L}_{x=\text{inp}[i]}$  for each  $i$ -th input wire  $x$ .

$\text{Garble}(\text{sk} = (\mathsf{L}, \mathbb{G}_q, g), \mathcal{C})$ :

- Sample  $\mathsf{L}_{x=b} \xleftarrow{\$} \{0,1\}^\lambda$  for every non-input independent wire  $x$  and  $b \in \{0,1\}$ . Sample  $\mathsf{K}_x \xleftarrow{\$} \mathbb{Z}_q^*$  for each cable  $\mathbf{x}^W$ . Sample  $\Gamma_{i,b} \xleftarrow{\$} \mathbb{Z}_q^*$  for every  $i \in [W_{\max}]$  and  $b \in \{0,1\}$ , where  $W_{\max}$  is the maximum width of any cable. Compute the labels  $\mathsf{L}_{x_i=b} = g^{\mathsf{K}_x \Gamma_{i,b}}$  for every subwire  $x_i$  of every cable  $\mathbf{x}^W$  and  $b \in \{0,1\}$ .

- For each gate  $\text{gid}$ , compute the GC material  $\widetilde{\text{Gates}}[\text{gid}]$  based on its gate type:

– **Boolean**  $z \leftarrow f(x, y)$ :

$$\widetilde{\text{Gates}}[\text{gid}] \leftarrow \{\text{Enc}_{\mathsf{L}_{x=a}, \mathsf{L}_{y=b}}(\mathsf{L}_{z=f(a,b)}) \mid a, b \in \{0,1\}\}$$

– **Group**  $y_i \xleftarrow{\text{grp}} x$ :

$$\widetilde{\text{Gates}}[\text{gid}] \leftarrow \{\text{Enc}_{\mathsf{L}_{x=a}}(\mathsf{L}_{y_i=a}) \mid a \in \{0,1\}\}$$

– **Ungroup**  $y \xleftarrow{\text{ungrp}} x_i$ :

$$\widetilde{\text{Gates}}[\text{gid}] \leftarrow \{\text{Enc}_{\mathsf{L}_{x_i=a}}(\mathsf{L}_{y=a}) \mid a \in \{0,1\}\}$$

– **Switch**  $\mathbf{x}^W \xrightarrow{c} \mathbf{y}^W$ :

$$\widetilde{\text{Gates}}[\text{gid}] \leftarrow \text{Enc}_{\mathsf{L}_{c=0}}(\mathsf{K}_x^{-1} \cdot \mathsf{K}_y)$$

- Let  $\widetilde{\text{Out}}[i] \leftarrow \text{Enc}_{\mathsf{L}_{y=0}}(0)$  for each  $i$ -th output wire  $y$ .

- Return  $\widetilde{\mathcal{C}} = (\mathcal{C}, \mathbb{G}_q, \widetilde{\text{Gates}}, \widetilde{\text{Out}})$

Figure 3: Our garbling scheme based on DDH (continued in Figure 4).

$\text{Eval}(\widetilde{\mathcal{C}} = (\mathcal{C}, \mathbb{G}_q, \widetilde{\text{Gates}}, \widetilde{\text{Out}}), \widetilde{\text{inp}})$ :

- Let  $\mathsf{L}_x \leftarrow \widetilde{\text{inp}}[i]$  for each  $i$ -th input wire  $x$ . Evaluate every gate  $\text{gid}$  in the topological order specified by the evaluation rules in Table 4:

- **Boolean**  $z \leftarrow f(x, y)$ :

For each entry  $R \in \widetilde{\text{Gates}}[\text{gid}]$ , let  $m \leftarrow \text{Dec}_{\mathsf{L}_x, \mathsf{L}_y}(R)$  and set  $\mathsf{L}_z \leftarrow m$  if  $m \neq \perp$ .

- **Group**  $y_i \xleftarrow{\text{grp}} x$ :

For each entry  $R \in \widetilde{\text{Gates}}[\text{gid}]$ , let  $m \leftarrow \text{Dec}_{\mathsf{L}_x}(R)$  and set  $\mathsf{L}_{y_i} \leftarrow m$  if  $m \neq \perp$ .

- **Ungroup**  $y \xleftarrow{\text{ungrp}} x_i$ :

For each entry  $R \in \widetilde{\text{Gates}}[\text{gid}]$ , let  $m \leftarrow \text{Dec}_{\mathsf{L}_{x_i}}(R)$  and set  $\mathsf{L}_y \leftarrow m$  if  $m \neq \perp$ .

- **Switch**  $\mathbf{x}^W \xleftarrow{c} \mathbf{y}^W$ :

Let  $m \leftarrow \text{Dec}_{\mathsf{L}_c}(\widetilde{\text{Gates}}[\text{gid}])$ . Skip the gate if  $m = \perp$ . Otherwise, for each  $i \in [W]$ , set  $\mathsf{L}_{y_i} \leftarrow (\mathsf{L}_{x_i})^m$  if  $\mathsf{L}_{x_i}$  is known, and set  $\mathsf{L}_{x_i} \leftarrow (\mathsf{L}_{y_i})^{m^{-1}}$  if  $\mathsf{L}_{y_i}$  is known.<sup>†</sup>

- For each  $i$ -th output wire  $y$ , let  $m \leftarrow \text{Dec}_{\mathsf{L}_y}(\widetilde{\text{Out}}[i])$ . If  $m \neq \perp$ , set  $\text{out}[i] \leftarrow 0$ ; else set  $\text{out}[i] \leftarrow 1$ .

- Return  $\text{out}$

<sup>†</sup> Instead of computing the exponentiation repeatedly, the evaluator can keep track of an exponent pending to be applied, and perform modular multiplications on the exponent until reaching an Ungroup gate.

Figure 4: Our garbling scheme based on DDH (continued from Figure 3).

$\lambda$  is the security parameter. Moreover, we assume that  $\text{Dec}$  outputs  $\perp$  with overwhelmingly high probability if the key is incorrect. Such an encryption scheme can be constructed directly from ElGamal [ElG85] by

- using the private key in ElGamal as the symmetric key for  $\Pi$ , and

- adding a  $\lambda$ -bit nonce to the plaintext  $m$ , and let  $\text{Dec}$  output  $\perp$  if the decrypted nonce doesn't match.

In addition, we use the notation  $\text{Enc}_{k_1, k_2}(m)$  as a shorthand for the double encryption  $\text{Enc}_{k_1}(\text{Enc}_{k_2}(m))$ , and  $\text{Dec}_{k_1, k_2}(c)$  as a shorthand for the following operations:

- If  $\text{Dec}_{k_2}(c) = \perp$ , then return  $\perp$ .

- Else return  $\text{Dec}_{k_1}(\text{Dec}_{k_2}(c))$ .

**Full construction.** We present our full garbling scheme in Figure 3 and Figure 4. Without loss of generality, we assume that all the input wires are independent wires.

On a high level, the Boolean, Group, Ungroup gates are garbled similar to Yao's garbled circuit [Yao86], except that we encode cables with our custom labels. For the Switch gates, we encrypt the quotient of the two cable keys under the zero label of the control wire. If the control wire is

zero, the evaluator can decrypt the quotient and hence learn the labels of one cable from the other, which matches our evaluation rules for the Switch gates in Table 4. Otherwise, the decryption fails, and the evaluator learns that the Switch gate is inactive. Since the circuit is well-formed, the evaluator can eventually compute the label corresponding to the unique value of each wire.

### 4.3 Analysis

**Efficiency.** Each gate or output wire of  $\mathcal{C}$  adds an  $O(1)$ -row garbled truth table to the garbled circuit, with each row being an  $O(\lambda)$ -bit ciphertext string. Therefore, each gate or output wire incurs  $O(\lambda)$  bits of communication, and the total communication cost of  $\mathcal{C}$  is  $O(\lambda \cdot |\mathcal{C}|)$  bits. In comparison, prior works [HKO23, Hea24] require  $O(\lambda \cdot W)$  bits to garble a circuitry equivalent to our Switch gate, where  $W$  is the width of the cables the Switch connects to.

**Correctness.** Given the input labels to each gate, the evaluator can identify the correct row to decrypt in garbled truth table and learn the output wire’s label with overwhelmingly high probability. It is straightforward to check that the truth tables agree to the evaluation rules in Table 4 for each gate. By dynamic well-formedness (Definition 3.1), the evaluator learns a unique label  $L_x$  that matches the value of each wire  $x$ , and can decode the value of each  $i$ -th output wire  $y$  by checking whether  $\text{Out}[i]$  can be decrypted successfully with the key  $L_y$ .

**Security.** We prove the security of the garbling scheme assuming DDH. First, we introduce a simple lemma.

**Lemma 4.3.** *Let  $g$  be a generator of a DDH group  $\mathbb{G}_q$  with prime order  $q$  and security parameter  $\lambda$ , and  $k, \gamma_0, \gamma_1 \xleftarrow{\$} \mathbb{Z}_q^*$ . Then, the ensemble of tuple  $\bar{T} = (g, g^{\gamma_0}, g^{\gamma_1}, g^{k \cdot \gamma_0}, g^{k \cdot \gamma_1})$  is computationally indistinguishable from the ensemble  $\bar{T}' = (g, g^{\gamma_0}, g^{\gamma_1}, R_0, R_1)$ , where  $R_0, R_1 \xleftarrow{\$} \mathbb{G}_q$ .*

*Proof.* By the DDH assumption,  $(g, g^k, g^\gamma, g^{k \cdot \gamma})$  is computationally indistinguishable from  $(g, g^k, g^\gamma, R)$ , for uniformly random  $\gamma$  and  $R$ . Therefore,

$$\begin{aligned} \{\bar{T}\}_{\lambda \in \mathbb{N}} &= \left\{ \left( g, g^k, g^{\gamma_0}, (g^{\gamma_0})^{\gamma_r}, g^{k \cdot \gamma_0}, (g^{k \cdot \gamma_0})^{\gamma_r} \right) \mid \gamma_r \xleftarrow{\$} \mathbb{Z}_q^* \right\}_{\lambda \in \mathbb{N}} \\ &\stackrel{c}{\approx} \left\{ \left( g, g^k, g^{\gamma_0}, (g^{\gamma_0})^{\gamma_r}, R_0, (g^{k \cdot \gamma_0})^{\gamma_r} \mid \gamma_r \xleftarrow{\$} \mathbb{Z}_q^* \right) \right\}_{\lambda \in \mathbb{N}} \\ &= \left\{ \left( g, g^{\gamma_0}, g^{\gamma_1}, R_0, g^{k \cdot \gamma_1} \right) \right\}_{\lambda \in \mathbb{N}} \\ &\stackrel{c}{\approx} \{(g, g^{\gamma_0}, g^{\gamma_1}, R_0, R_1)\}_{\lambda \in \mathbb{N}} = \{\bar{T}'\}_{\lambda \in \mathbb{N}} \end{aligned}$$

□

Now, we present the main theorem. At a high level, we follow the proof of Yao’s garbled circuit [Yao86, LP09], replacing the labels of wires with random labels in the order of evaluation, and apply additional techniques to handle Switch gates and subwire labels.

**Theorem 4.4** (Security of the garbling scheme in the plain model). *Assuming DDH, The construction in Figure 3 and 4 is a secure garbling scheme for the family of strictly well-formed SIMD tri-state circuit w.r.t. the leakage function  $\text{controls}(\cdot, \cdot)$  as defined below: given a well-formed SIMD tri-state circuit  $\mathcal{C}$  and input  $\text{inp}$ ,  $\text{controls}(\mathcal{C}, \text{inp})$  outputs the values on all the control wires of the Switch gates when evaluating  $\mathcal{C}$  over  $\text{inp}$ .*

$\text{Sim}(1^\lambda, \text{ctrl}, \text{out}, \mathcal{C})$ :

- Select a prime-order DDH group  $\mathbb{G}_q$  with security parameter  $\lambda$ , and a generator  $g$  of the group, same as  $\text{Gen}$ .

- Sample  $\mathsf{L}_x, \mathsf{L}'_x \xleftarrow{\$} \{0,1\}^\lambda$  for every independent wire  $x$ . Let  $\widetilde{\text{inp}}[i] \leftarrow \mathsf{L}_{x_{\text{in}}}$  for each  $i$ -th input wire  $x_{\text{in}}$ .

- For every union of cables connected by active Switch gates, sample union-wise labels  $\mathsf{L}_{U_i}, \mathsf{L}'_{U_i} \xleftarrow{\$} \mathbb{G}_q$  for every offset  $i \in [W]$ , where  $W$  is the width of each cable in the union. For every cable, sample  $\mathsf{K}_x \xleftarrow{\$} \mathbb{Z}_q^*$ , and compute its subwires' labels as  $\mathsf{L}_{x_i} = (\mathsf{L}_{U_i})^{\mathsf{K}_x}$  and  $\mathsf{L}'_{x_i} = (\mathsf{L}'_{U_i})^{\mathsf{K}_x}$ .

- For each gate  $\text{gid}$ , compute the GC material  $\widetilde{\text{Gates}}[\text{gid}]$  based on its gate type:

- **Boolean**  $z \leftarrow f(x, y)$ :

$$\widetilde{\text{Gates}}[\text{gid}] \leftarrow \{\text{Enc}_{l_x, l_y}(\mathsf{L}_z) \mid l_x \in \{\mathsf{L}_x, \mathsf{L}'_x\}, l_y \in \{\mathsf{L}_y, \mathsf{L}'_y\}\}$$

– **Group**  $y_i \xleftarrow{\text{grp}} x$ :