# **PSP VFPU instruction set documentation**

# Introduction

This document describes how the PSP VFPU instruction set operates. We attempted to collect all the knowledge available in the community and put it together in a document that can be used as a reference for developers and enthusiasts.

The goal is to describe the behaviour of the hardware unit with as much detail as possible in a way that every statement can be verified. For this reason, every functional detail described in the docs must have a test that validates it. Of course some things are harder to validate (like hardware bugs) so there's some statements that won't have tests for them at this time.

## MIPS allegrex CPU

The Allegrex CPU is a MIPS CPU based on the MIPS II architecture. This is a 32 bit CPU and architecture that has many similarities with other CPUs of the same architecture. However, if we only focus on the instruction set, the main differences with other CPUs in the MIPS II family would be:

- Lack of 64 bit FPU support (only single float support).

- Lack of MMU/TLB (only certain memory protections are available).

- Some extra MIPS32r2 instructions (mostly arithmetic and bit manipulation).

- Other COP0 instructions, some borrowed from MIPS32

- Lack of *Coprocessor 3* and custom *Coprocessor 2* (VFPU)

Most of the extra instructions that are present in the CPU are identical to their MIPS32 counterparts. In some cases though, the encoding is slightly different.

## VFPU unit

The PSP VFPU is a coprocessor unit that can perform vector/matrix float and integer operations on a set of 128 bit registers. It features dedicated units to perform the most usual operations that 3D videogames require.

## Register set

The CPU features 128 registers, each of them 32 bit wide. Most of the time they are interpreted as IEEE-754 compliant floating point registers, although some instructions will interpret them as integers (or other formats such as 8/16 bit packed integers). The registers can be addressed individually but also in a more powerful way by grouping them as vectors or matrices.

Registers will usually be represented in their matrix layout. The VFPU has 8 matrices, each of them containing 16 elements (4 rows by 4 columns). For each of the 8 total available matrices, the elements are arranged in the following fashion (x represents the matrix number, 0 to 7):

Single 32 bit elements

|      |      |      |      |

|------|------|------|------|

| SX00 | SX10 | SX20 | SX30 |

| SX01 | SX11 | SX21 | SX31 |

| SX02 | SX12 | SX22 | SX32 |

| SX03 | SX13 | SX23 | SX33 |

When the registers are referenced as vectors, they are grouped as rows and columns of a given matrix. This is important since it means that a vector is composed of elements from a single matrix and cannot access elements across multiple matrices. There's 2D, 3D and 4D vectors, usually called pair, trio and quad respectively. Single elements can be viewed as 1D vectors, and most instructions are available in all four possible vector sizes (which makes the instruction set very uniform). Not all access patterns are possible: pair and trio registers have 128 possible addressing modes while quad has only 64. The available patterns are described as follows:

2D vector rows

|      |  |      |  |

|------|--|------|--|

| RX00 |  | RX20 |  |

| RX01 |  | RX21 |  |

| RX02 |  | RX22 |  |

| RX03 |  | RX23 |  |

3D vector rows

|  |      |  |  |

|--|------|--|--|

|  | RX00 |  |  |

|  | RX01 |  |  |

|  | RX02 |  |  |

|  | RX03 |  |  |

3D vector rows

|  |  |      |  |

|--|--|------|--|

|  |  | RX10 |  |

|  |  | RX11 |  |

|  |  | RX12 |  |

|  |  | RX13 |  |

4D vector rows

|  |      |  |  |

|--|------|--|--|

|  | RX00 |  |  |

|  | RX01 |  |  |

|  | RX02 |  |  |

|  | RX03 |  |  |

2D vector cols

|      |      |      |      |

|------|------|------|------|

| CX00 | CX10 | CX20 | CX30 |

|      |      |      |      |

| CX02 | CX12 | CX22 | CX32 |

|      |      |      |      |

3D vector cols

|      |      |      |      |

|------|------|------|------|

|      |      |      |      |

| CX00 | CX10 | CX20 | CX30 |

|      |      |      |      |

|      |      |      |      |

3D vector cols

|      |      |      |      |

|------|------|------|------|

|      |      |      |      |

|      |      |      |      |

| CX01 | CX11 | CX21 | CX31 |

|      |      |      |      |

4D vector cols

|      |      |      |      |

|------|------|------|------|

|      |      |      |      |

| CX00 | CX10 | CX20 | CX30 |

|      |      |      |      |

|      |      |      |      |

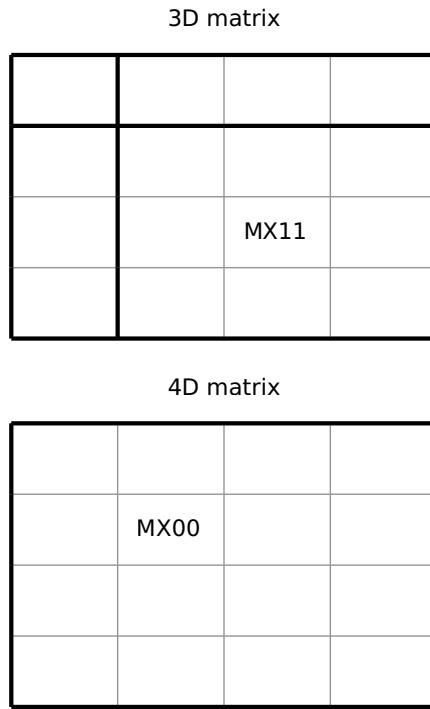

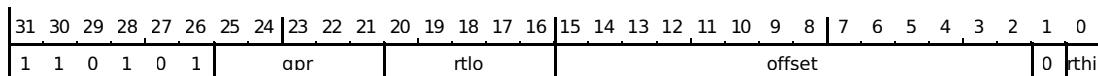

Matrix addressing is similar to vectors: registers can be read vertically or horizontally. That means matrices can be accessed in a row major and column major mode (ie. by

accessing them as a set of rows or columns). Similarly there's three possible sizes: 2x2, 3x3 and 4x4, containing 4, 9 and 16 registers respectively. Again not all addressing patterns are available, having 64 possible addressing modes for 2x2 and 3x3 matrices, but only 16 for 4x4 matrices. These are:

2D matrix

|      |  |      |  |

|------|--|------|--|

| MX00 |  | MX20 |  |

|      |  |      |  |

| MX02 |  | MX22 |  |

|      |  |      |  |

3D matrix

|      |  |  |  |

|------|--|--|--|

|      |  |  |  |

|      |  |  |  |

| MX00 |  |  |  |

|      |  |  |  |

3D matrix

|      |  |  |  |

|------|--|--|--|

|      |  |  |  |

|      |  |  |  |

| MX10 |  |  |  |

|      |  |  |  |

3D matrix

|      |  |  |  |

|------|--|--|--|

|      |  |  |  |

|      |  |  |  |

| MX01 |  |  |  |

|      |  |  |  |

There's also a small set of eight "control" registers that are used for a variety of things, such as prefix state, comparison flag bits, etc. These registers are defined as follow:

- Reg 128 (VFPU\_PFXS): holds the rs prefix value.

- Reg 129 (VFPU\_PFXT): holds the rt prefix value.

- Reg 130 (VFPU\_PFXD): holds the rd prefix value.

- Reg 131 (VFPU\_CC): holds the condition code value.

- Reg 135 (VFPU\_REV): read only register with VFPU revision information.

- Regs 136 to 147 (VFPU\_RCX0 to VFPU\_RCX7): Pseudorandom generator state.

Some of these registers are never accessed directly but rather using some VFPU instructions (ie. prefixes, condition code, etc). However these can be read and written in some useful cases, for instance thread context saving and restoration (so that the VFPU state is preserved across thread rescheduling).

## Register hazards

Most CPUs have what's called "hazard detection logic", which tracks register reads and writes so that things happen in the right order and results actually make sense. In the VFPU this is also the case, however some operations are quite complex and can be complex to track.

Control registers seem to have some hazards, for instance "mfvc" instruction has a one cycle hazard with any previous vcmp instruction. That means a vnop or some other VFPU instruction should be inserted between a vcmp and mfvc instruction pair to get the right VFPU\_CC value.

Some VFPU instructions (mostly dealing with matrices and transformations) require that the input and output registers do not overlap. This has to do with how the hardware performs the operations internally: the VFPU can perform most vector-vector operations in a native way, but matrix operations seem to be decomposed into series of vector-vector operations (ie. a vmmul seems to be a sequence of vtfm operations). Since the

results are only partial, the inputs are overwritten before the CPU can even read them, causing incorrect results for the operation.

The affected instructions are divided in two groups, a group that does not allow any sort of overlap, and another group that allows some limited overlap. Instructions `vmmul`, `vtfm2/3/4`, `vhtfm2/3/4`, `vqmul` and `vcrsp` do not allow any sort of overlap between input and output registers. These instructions perform operations by repeating a dot product operation multiple times, which results in partial updates of the output register. This partial updates overwrite the input register causing the result to be incorrect.

Instructions that allow partial overlaps are `vsin`, `vcos`, `vasin`, `vnsin`, `vexp2`, `vrexp2`, `vlog2`, `vsqrt`, `vrsq`, `vrcp`, `vnrcp`, `vdiv`, `vmscl` and `vmmov`. Single versions (.s) are not affected by this restriction. These instructions are also internally decomposed into a bunch of smaller operations (for instance trigonometric operations are decomposed into a series of single (.s) operations). The registers are allowed to overlap as long as they are compatible in terms of element count and access "direction" (ie. a matrix must be read using the same mode).

### Examples

```

vmscl.p M000, M022, S100      # No overlap, always OK

vmscl.p M000, M000, S100      # M000 overlaps with itself, OK

vmscl.p M000, E000, S100      # Invalid overlap, matrix order is different

vmscl.t M000, M011, S100      # Overlapping registers are not identical

vcos.q R000, C000            # Invalid overlap (one element only)

vcos.q R000, R000            # Identical overlap, OK

```

## Floating point format

Although the FPU seems IEEE-754 compliant, it has a couple of non-standard features that break this compatibility. Its rounding mode is hardwired to "round to nearest" mode, so that users cannot choose another rounding mode. It also lacks support for denormal numbers (also called subnormals): when an operation produces a subnormal number, it rounds it to zero. If the input of an operation is a denormal number, it will also be treated as zero.

See the `ieee754-fun.c` file for tests.

## Instruction execution

The VFPU is a pipelined CPU with an issue width of one. That means that instructions take multiple cycles to execute, since they execute partially during each cycle, and a maximum of one new instruction begins execution each cycle. Instructions that block the pipeline for more than one cycle can be identified by having a throughput different than one. These block the pipeline for a certain number of cycles before a new instruction can enter it.

An instruction usually begins executing whenever its input registers are ready, that is, any previous instruction writing those registers have fully completed their execution. For this reason it is important to closely observe the instruction latency, measured in cycles, since an instruction might have to wait for its inputs to become available, reducing

efficiency. A common strategy is to interleave non-dependant instructions to hide latency and avoid wasting CPU cycles.

The pipeline structure looks more or less as follows:

- Register read

- Input prefix operations

- VFPU operation (arithmetic, logic)

- Output prefix operation

- Register write

Prefix operations allow to perform certain operations on the inputs before the actual instruction operation and some other operations on the output.

## Prefix operations

VFPU operations can operate on one or two inputs (`rs` and `rt`) and one output (`rd`). The input values can be pre-processed by using the `VFPU_PFXS` and `VFPU_PFXT` registers (and therefore `vpxs` and `vpxt` instructions). The result of the operation being written to `rd` can be post-processed by using the `VFPU_PFXD` register (`vpxd` instruction).

Valid operations for input registers are:

- Sign change (negation)

- Absolute value

- Swizzle (rearranging elements in a row/col)

- Override element with constant value.

Operations available to the output register post-processing are:

- Value clamping (to ranges 0..1 or -1..1)

- Write masking (disable register write)

There's some restrictions on their usage. The assembler will signal an error should you violate any of the restrictions.

- Constant values can only be 0, 1, 2, 3,  $1/2$ ,  $1/3$ ,  $1/4$ ,  $1/6$  or any of their negative counterparts

- Swizzle cannot extend beyond the operand size (ie. you cannot use .z with a an instruction that uses single or pair elements).

A few examples to showcase input prefixes:

```

# Sign change prefix

vmul.p R000, R001, R002[-x,-y]      # Multiplies two rows negating one of the inputs

#  $S000 = S001 * -S002; S010 = S011 * -S012$

vfad.q R000, R001[x,-y,z,-w]        # Funnel-add all elements with some changed signs

#  $S000 = S001 - S011 + S021 - S031$

# Absolute value prefix

vdot.p S000, R001[|x|,|y|], R002  # Dot product with forced absolute value for R001

#  $S000 = |S001| * S002 + |S011| * S012$

```

```

# Negative and absolute value prefixes

vdot.p S000, R001[-|x|,-|y|], R002  # Dot product with forced negative values

# S000 = -|S001| * S002 - |S011| * S012

# Swizzle prefix

vdot.q R000, R001, R002[x,y,x,y]  # Multiplies with repeating values

# S000 = S001 * S002;  S010 = S011 * S012

# S020 = S021 * S002;  S030 = S031 * S012

# Constant value prefixes

vdot.t R000, R001, R002[1,2,3]  # Second operand ignored, overrides to (1,2,3)

# S000 = S001 + S011 * 2 + S021 * 3

vdot.t R000, R001, R002[x,-2,-y]  # Mix swizzle and constant elements

# S000 = S001 * S002 - S011 * 2 - S021 * S012

```

Some more examples for output prefixes.

```

vmul.p R000[[-1:1],[-1:1]], R001, R002  # Multiplies with output saturation

# S000 = min(1.0f, max(-1.0f, S001 * S002))

# S010 = min(1.0f, max(-1.0f, S011 * S012))

```

Adding a prefix modifier to an operand will result in vpxfs/t/d instructions being emitted before the actual instruction. This syntax exists just to make assembly coding more comfortable to the user. When using the disassembler the prefix instructions will be clearly visible.

```

# The following operand-decorated instruction:

vmul.q R000, R100[x,y,x,y], R200[-x,-y,z,w]

# is actually encoded as a sequence of instructions:

vpxfs [x,y,x,y]

vpxft [-x,-y,z,w]

vmul.q R000, R100, R200

```

Prefix instructions consume one cycle and have no visible latency (the "decorated" instruction doesn't have to wait any extra cycles). In some cases it might be faster to not use prefixes and use other instructions (vcst, vabs, vneg, vsat0/1 are some similar alternatives), particularly when optimizing for throughput. The advantage of using prefixes is that latency is kept low (since they have no latency and the extra operation is "included" in the instruction pipeline).

# Allegrex Instructions

## Bit manipulation instructions

The following instructions exist in the Allegrex CPU and share the same MIPS32 encodings:

- *seb*: Sign extend byte (byte to word signed extension)

- *seh*: Sign extend half-word (half-word to word signed extension)

- *ext*: Extract bit field (extract a bit field in a zeroed register)

- *ins*: Insert bit field (insert lower bits into another register)

- *wsbh*: Swap bytes within a half-word

Other instructions that are borrowed from MIPS32 but have a different encoding are:

- *clo*: Count leading ones (uses some unused **SPECIAL** encodings)

- *clz*: Count leading zeros (uses some unused **SPECIAL** encodings)

The bit manipulation Allegrex specific instructions are:

- *wsbw*: Swap bytes in word (uses **BSHFL** encoding adjacent to *wsbh*)

- *bitrev*: Reverse bits in a word (uses unused **BSHFL** encoding)

## Arithmetic-Logical instructions

Allegrex features some instructions present in MIPS32 and MIPS32r2 with identical encoding to these:

- *rotr*: Rotate word right by a fixed amount

- *rotrv*: Rotate word right by a variable amount

- *movz*: Conditional register move on zero

- *movn*: Conditional register move on non-zero

Other instructions that have some particular encoding are multiply-accumulate instructions. Some overlap with MIPS R4010 encodings and some others just use unused encodings. They all use unused **SPECIAL** opcodes:

- *madd*: Signed multiply-accumulate integer

- *maddu*: Unsigned multiply-accumulate integer

- *msub*: Signed multiply-subtract integer

- *msubu*: Unsigned multiply-subtract integer

There's also two novel Allegrex instructions that are used to perform faster compare-and-move operations. These use free **SPECIAL** opcodes as well:

- *min*: Selects smallest (signed) value between two registers.

- *max*: Selects greatest (signed) value between two registers.

# bvf

VFPU branch on false

|    |    |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

|----|----|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20     | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | vfbucc | 0  | 0  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | offset |

## Syntax

bvf imm3, offset

## Description

Branch on VFPU CC register being false

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 4 cycles

# **bvfl**

**VFPU likely branch on false**

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |        |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |        |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | offset |

## Syntax

`bvfl imm3, offset`

## Description

Branch on VFPU CC register being false (likely)

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 4 cycles

# bvt

## VFPU branch on true

|    |    |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

|----|----|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20     | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | vfbucc | 0  | 1  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | offset |

## Syntax

bvt imm3, offset

## Description

Branch on VFPU CC register being true

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 4 cycles

# bvtl

VFPU likely branch on true

|    |    |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

|----|----|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20     | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | vfpucc | 1  | 1  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | offset |

## Syntax

bvtl imm3, offset

## Description

Branch on VFPU CC register being true (likely)

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 4 cycles

# mtvc

## Move GPR to VFPU control register

|    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 1  |    | apr |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## Syntax

mtvc rt, \$ccreg

## Description

Writes the contents of a CPU general purpose register to the specified VFPU control register

## Allowed prefixes

- rt: Not supported

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |       |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

| 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 1  |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   |   |   |   |   |   | ccrea |

## Syntax

mfvc rt, \$ccreg

## Description

Writes the contents of the specified VPFU control register into a CPU general purpose register

## Hazards

The instruction does not have interlocks, so the result of a vcmp instruction is only available one cycle later. You will need to interleave at least one VFPU instruction between a vcmp and mfvc (ie. a vnop).

## Allowed prefixes

- rt: Not supported

# vmtvc

## Move vector register to VFPU control register

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |    |       |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|-------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0     |

| 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |    |    |    |    |    |   |   |   |   |   |   |   |   | rs | ccrea |

### Syntax

vmtvc \$ccreg, rs

### Description

Writes the contents of a VFPU vector general to the specified VFPU control register

### Allowed prefixes

- rs: Not supported

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |       |    |    |    |    |    |   |   |   |   |    |   |   |   |   |   |  |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|----|----|----|----|----|---|---|---|---|----|---|---|---|---|---|--|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |  |  |

| 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | ccrea |    | 0  |    |    |    |   |   | 0 |   | rd |   |   |   |   |   |  |  |

## Syntax

vmfvc rd, \$ccreg

## Description

Writes the contents of the specified VPFU control register into a VFPU vector register

## Hazards

The instruction does not have interlocks, so the result of a previous vcmp instruction is only available one cycle later. You will need to interleave at least one VFPU instruction between a vcmp and mfvc (ie. a vnop).

## Allowed prefixes

- rd: Not supported

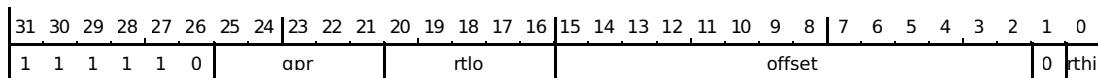

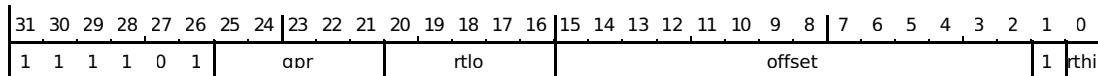

|    |    |    |    |    |    |    |    |     |    |    |      |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |      |  |

|----|----|----|----|----|----|----|----|-----|----|----|------|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|------|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |  |

| 1  | 1  | 0  | 0  | 1  | 0  |    |    | opr |    |    | rtlo |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | rthi |  |

## Syntax

lv.s rd, imm14(rt)

## Description

Performs a 4 byte memory load to a VFPU register. Address must be 4 byte aligned or a fault is generated.

## Allowed prefixes

- rt: Not supported

- rd: Not supported

lv.q

## Load VFPU quad element

## Syntax

lv.q rd, imm14(rt)

## Description

Performs a 16 byte memory load to a VFPU quad register. Address must be 16 byte aligned or a fault is generated.

## Allowed prefixes

- rt: Not supported

- rd: Not supported

## Syntax

lvl.q rd, imm14(rt)

## Description

Performs a 16 byte left unaligned memory load to a VFPU quad register. Instruction ignores the two LSB (forces them to zero), so the address is assumed aligned to 4 bytes. This instruction is similar to MIPS LWL instruction: loads the most significant elements from the specified address leaving the other elements unchanged. Users can use `ulv.q` pseudoinstruction to generate a sequence of `lvl.q` and `lvr.q` instructions in order to load unaligned data. You can check `psp-tests/manual/memops.c` to see examples on how the instruction behaves.

## Bugs

The instruction has an errata on PSP-1000 models that causes FPU register corruption (these are the MIPS CPU FPU registers, not the VFPU registers). The bottom 5 bits of the VFPU destination register determine which FPU register will be corrupted. A workaround is to assume the side effect (ie. mark the register are clobbered).

## Allowed prefixes

- rt: Not supported

- rd: Not supported

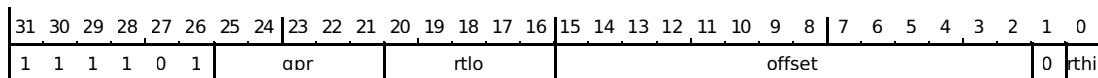

|    |    |    |    |    |    |    |    |     |    |    |      |    |    |    |    |    |    |    |    |    |    |   |        |   |   |   |   |   |   |   |      |  |

|----|----|----|----|----|----|----|----|-----|----|----|------|----|----|----|----|----|----|----|----|----|----|---|--------|---|---|---|---|---|---|---|------|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |  |

| 1  | 1  | 0  | 1  | 0  | 1  |    |    | opr |    |    | rtlo |    |    |    |    |    |    |    |    |    |    |   | offset |   |   |   |   |   |   | 1 | rthi |  |

## Syntax

```

lvr.q rd, imm14(rt)

```

## Description

Performs a 16 byte right unaligned memory load to a VFPU quad register. Instruction ignores the two LSB (forces them to zero), so the address is assumed aligned to 4 bytes. This instruction is similar to MIPS LWR instruction: loads the least significant elements from the specified address leaving the other elements unchanged. Users can use `ulv.q` pseudoinstruction to generate a sequence of `lvl.q` and `lvr.q` instructions in order to load unaligned data. You can check `psp-tests/manual/memops.c` to see examples on how the instruction behaves.

## Bugs

The instruction has an errata on PSP-1000 models that causes FPU register corruption (these are the MIPS CPU FPU registers, not the VFPU registers). The bottom 5 bits of the VFPU destination register determine which FPU register will be corrupted. A workaround is to assume the side effect (ie. mark the register are clobbered).

## Allowed prefixes

- rt: Not supported

- rd: Not supported

## Syntax

sv.s rs, imm14(rt)

## Description

Performs a 4 byte memory store from a VFPU register. Address must be 4 byte aligned or a fault is generated.

## Allowed prefixes

- rt: Not supported

- rs: Not supported

**SV.q****Store VFPU quad element**

## Syntax

sv.q rs, imm14(rt)

## Description

Performs a 16 byte memory store from a VFPU quad register. Address must be 16 byte aligned or a fault is generated.

## Allowed prefixes

- rt: Not supported

- rs: Not supported

## Syntax

svl.q rs, imm14(rt)

## Description

Performs a 16 byte left unaligned memory store from a VFPU quad register. Instruction ignores the two address LSB (forces them to zero), so the address is assumed aligned to 4 bytes. This instruction is similar to MIPS SWL instruction: stores the most significant part of the elements to the specified address leaving any other elements unchanged. Users can use `usv.q` pseudoinstruction to generate a sequence of `svl.q` and `svr.q` instructions in order to store unaligned data. You can check `psp-tests/manual/memops.c` to see examples on how the instruction behaves.

## Allowed prefixes

- rt: Not supported

- rs: Not supported

# Svr.q

## Store right VFPU quad element

## Syntax

svr.q rs, imm14(rt)

## Description

Performs a 16 byte right unaligned memory store from a VFPU quad register. Instruction ignores the two address LSB (forces them to zero), so the address is assumed aligned to 4 bytes. This instruction is similar to MIPS SWR instruction: stores the least significant part of the elements to the specified address leaving any other elements unchanged. Users can use `usv.q` pseudoinstruction to generate a sequence of `svl.q` and `svr.q` instructions in order to store unaligned data. You can check `psp-tests/manual/memops.c` to see examples on how the instruction behaves.

## Allowed prefixes

- rt: Not supported

- rs: Not supported

# vadd.s

## Add elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | rt | 0  | rs | 0  | rd |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

## Syntax

vadd.s rd, rs, rt

## Description

Performs element-wise floating point addition

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] + rt[0]

```

# vadd.p

Add elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | rt | 0  | rs | 1  | rd |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

## Syntax

vadd.p rd, rs, rt

## Description

Performs element-wise floating point addition

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] + rt[0]

rd[1] = rs[1] + rt[1]

```

# vadd.t

Add elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vadd.t rd, rs, rt

## Description

Performs element-wise floating point addition

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] + rt[0]

rd[1] = rs[1] + rt[1]

rd[2] = rs[2] + rt[2]

```

# vadd.q

Add elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |    | rs |    | 1  |    | rd |   |   |   |   |   |   |   |   |   |

## Syntax

vadd.q rd, rs, rt

## Description

Performs element-wise floating point addition

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] + rt[0]

rd[1] = rs[1] + rt[1]

rd[2] = rs[2] + rt[2]

rd[3] = rs[3] + rt[3]

```

# vsub.s

## Subtract elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vsub.s rd, rs, rt

## Description

Performs element-wise floating point subtraction

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] - rt[0]

```

# vsub.p

## Subtract elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vsub.p rd, rs, rt

## Description

Performs element-wise floating point subtraction

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] - rt[0]

rd[1] = rs[1] - rt[1]

```

# vsub.t

## Subtract elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vsub.t rd, rs, rt

## Description

Performs element-wise floating point subtraction

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] - rt[0]

rd[1] = rs[1] - rt[1]

rd[2] = rs[2] - rt[2]

```

# vsub.q

## Subtract elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vsub.q rd, rs, rt

## Description

Performs element-wise floating point subtraction

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] - rt[0]

rd[1] = rs[1] - rt[1]

rd[2] = rs[2] - rt[2]

rd[3] = rs[3] - rt[3]

```

# vmul.s

## Multiply elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vmul.s rd, rs, rt

## Description

Performs element-wise floating point multiplication

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] * rt[0]

```

# vmul.p

## Multiply elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vmul.p rd, rs, rt

## Description

Performs element-wise floating point multiplication

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] * rt[0]

rd[1] = rs[1] * rt[1]

```

# vmul.t

## Multiply elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vmul.t rd, rs, rt

## Description

Performs element-wise floating point multiplication

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] * rt[0]

rd[1] = rs[1] * rt[1]

rd[2] = rs[2] * rt[2]

```

# vmul.q

## Multiply elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vmul.q rd, rs, rt

## Description

Performs element-wise floating point multiplication

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] * rt[0]

rd[1] = rs[1] * rt[1]

rd[2] = rs[2] * rt[2]

rd[3] = rs[3] * rt[3]

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   |   |  |

## Syntax

vdiv.s rd, rs, rt

## Description

Performs element-wise floating point division

## Instruction performance

Throughput: 14 cycles/instruction

Latency: 17 cycles

## Register overlap compatibility

Output register can only overlap with input registers if they are identical

## Allowed prefixes

- rt: Full support (swizzle, abs(), neg() and constants)

- rs: Full support (swizzle, abs(), neg() and constants)

- rd: Full support (masking and saturation)

## Pseudocode

```

rd[0] = rs[0] / rt[0]

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  |    |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vdiv.p rd, rs, rt

## Description

Performs element-wise floating point division

## Instruction performance

Throughput: 28 cycles/instruction

Latency: 31 cycles

## Register overlap compatibility

Output register can only overlap with input registers if they are identical

## Allowed prefixes

- rt: Not supported

- rs: Not supported

- rd: Not supported

## Pseudocode

```

rd[0] = rs[0] / rt[0]

rd[1] = rs[1] / rt[1]

```

# vdiv.t

## Divide elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  |    |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vdiv.t rd, rs, rt

## Description

Performs element-wise floating point division

## Instruction performance

Throughput: 42 cycles/instruction

Latency: 45 cycles

## Register overlap compatibility

Output register can only overlap with input registers if they are identical

## Allowed prefixes

- rt: Not supported

- rs: Not supported

- rd: Not supported

## Pseudocode

```

rd[0] = rs[0] / rt[0]

rd[1] = rs[1] / rt[1]

rd[2] = rs[2] / rt[2]

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vdiv.q rd, rs, rt

## Description

Performs element-wise floating point division

## Instruction performance

Throughput: 56 cycles/instruction

Latency: 59 cycles

## Register overlap compatibility

Output register can only overlap with input registers if they are identical

## Allowed prefixes

- rt: Not supported

- rs: Not supported

- rd: Not supported

## Pseudocode

```

rd[0] = rs[0] / rt[0]

rd[1] = rs[1] / rt[1]

rd[2] = rs[2] / rt[2]

rd[3] = rs[3] / rt[3]

```

# vmin.s

Select smallest elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   |   |  |

## Syntax

vmin.s rd, rs, rt

## Description

Performs element-wise floating point  $\min(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fminf(rs[0], rt[0])

```

# vmin.p

Select smallest elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vmin.p rd, rs, rt

## Description

Performs element-wise floating point  $\min(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fminf(rs[0], rt[0])

rd[1] = fminf(rs[1], rt[1])

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vmin.t rd, rs, rt

## Description

Performs element-wise floating point  $\min(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fminf(rs[0], rt[0])

rd[1] = fminf(rs[1], rt[1])

rd[2] = fminf(rs[2], rt[2])

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vmin.q rd, rs, rt

## Description

Performs element-wise floating point  $\min(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fminf(rs[0], rt[0])

rd[1] = fminf(rs[1], rt[1])

rd[2] = fminf(rs[2], rt[2])

rd[3] = fminf(rs[3], rt[3])

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vmax.s rd, rs, rt

## Description

Performs element-wise floating point  $\max(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fmaxf(rs[0], rt[0])

```

# vmax.p

Select biggest elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vmax.p rd, rs, rt

## Description

Performs element-wise floating point max(rs, rt) operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fmaxf(rs[0], rt[0])

rd[1] = fmaxf(rs[1], rt[1])

```

# vmax.t

## Select biggest elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vmax.t rd, rs, rt

## Description

Performs element-wise floating point max(rs, rt) operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fmaxf(rs[0], rt[0])

rd[1] = fmaxf(rs[1], rt[1])

rd[2] = fmaxf(rs[2], rt[2])

```

# vmax.q

Select biggest elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vmax.q rd, rs, rt

## Description

Performs element-wise floating point  $\max(rs, rt)$  operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = fmaxf(rs[0], rt[0])

rd[1] = fmaxf(rs[1], rt[1])

rd[2] = fmaxf(rs[2], rt[2])

rd[3] = fmaxf(rs[3], rt[3])

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vscmp.s rd, rs, rt

## Description

Performs element-wise floating point comparison. The result is -1.0f, 0.0f or 1.0f depending on whether the input vs is less than vt, equal, or greater, respectively.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? -1f : rs[0] > rt[0] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vscmp.p rd, rs, rt

## Description

Performs element-wise floating point comparison. The result is -1.0f, 0.0f or 1.0f depending on whether the input vs is less than vt, equal, or greater, respectively.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? -1f : rs[0] > rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? -1f : rs[1] > rt[1] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   |   |  |

## Syntax

vscmp.t rd, rs, rt

## Description

Performs element-wise floating point comparison. The result is -1.0f, 0.0f or 1.0f depending on whether the input vs is less than vt, equal, or greater, respectively.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? -1f : rs[0] > rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? -1f : rs[1] > rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] < rt[2] ? -1f : rs[2] > rt[2] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vscmp.q rd, rs, rt

## Description

Performs element-wise floating point comparison. The result is -1.0f, 0.0f or 1.0f depending on whether the input vs is less than vt, equal, or greater, respectively.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? -1f : rs[0] > rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? -1f : rs[1] > rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] < rt[2] ? -1f : rs[2] > rt[2] ? 1.0f : 0.0f

rd[3] = rs[3] < rt[3] ? -1f : rs[3] > rt[3] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vsge.s rd, rs, rt

## Description

Performs element-wise floating point bigger-or-equal comparison. The result will be 1.0 if vs is bigger or equal to vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] >= rt[0] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |    |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   | rd |  |

## Syntax

vsge.p rd, rs, rt

## Description

Performs element-wise floating point bigger-or-equal comparison. The result will be 1.0 if vs is bigger or equal to vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] >= rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] >= rt[1] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vsge.t rd, rs, rt

## Description

Performs element-wise floating point bigger-or-equal comparison. The result will be 1.0 if vs is bigger or equal to vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] >= rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] >= rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] >= rt[2] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vsge.q rd, rs, rt

## Description

Performs element-wise floating point bigger-or-equal comparison. The result will be 1.0 if vs is bigger or equal to vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] >= rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] >= rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] >= rt[2] ? 1.0f : 0.0f

rd[3] = rs[3] >= rt[3] ? 1.0f : 0.0f

```

# vsIt.s

## Compare less-than and set elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   |   |  |

## Syntax

vsIt.s rd, rs, rt

## Description

Performs element-wise floating point less-than comparison. The result will be 1.0 if vs less than vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? 1.0f : 0.0f

```

# vslt.p

## Compare less-than and set elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |    |    |    | 0  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   | rd |

## Syntax

vslt.p rd, rs, rt

## Description

Performs element-wise floating point less-than comparison. The result will be 1.0 if vs less than vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |

## Syntax

vslt.t rd, rs, rt

## Description

Performs element-wise floating point less-than comparison. The result will be 1.0 if vs less than vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] < rt[2] ? 1.0f : 0.0f

```

# vslt.q

## Compare less-than and set elements

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vslt.q rd, rs, rt

## Description

Performs element-wise floating point less-than comparison. The result will be 1.0 if vs less than vt, otherwise will be zero.

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rs: Full support (swizzle, abs(), neg() and constants)

- rt: Full support (swizzle, abs(), neg() and constants)

## Pseudocode

```

rd[0] = rs[0] < rt[0] ? 1.0f : 0.0f

rd[1] = rs[1] < rt[1] ? 1.0f : 0.0f

rd[2] = rs[2] < rt[2] ? 1.0f : 0.0f

rd[3] = rs[3] < rt[3] ? 1.0f : 0.0f

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |    |

| 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   | rd |

## Syntax

vcrs.t rd, rs, rt

## Description

Performs a partial cross-product operation

## Instruction performance

Throughput: 1 cycles/instruction

Latency: 5 cycles

## Allowed prefixes

- rd: Full support (masking and saturation)

- rt: Not supported

- rs: Not supported

## Pseudocode

```

rd[0] = rs[1] * rt[2]

rd[1] = rs[2] * rt[0]

rd[2] = rs[0] * rt[1]

```

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 0 |   |   |   |   |   |   |   |  |  |

## Syntax

vcrsp.t rd, rs, rt

## Description

Performs a full cross-product operation

## Instruction performance

Throughput: 3 cycles/instruction

Latency: 9 cycles

## Register overlap compatibility

Output register cannot overlap with input registers

## Allowed prefixes

- rt: Not supported

- rs: Not supported

- rd: Not supported

## Pseudocode

```

rd[0] = rs[1] * rt[2] - rs[2] * rt[1]

rd[1] = rs[2] * rt[0] - rs[0] * rt[2]

rd[2] = rs[0] * rt[1] - rs[1] * rt[0]

```

# vqmul.q

## Quaternion multiplication

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 1  |    |    |    |    |    |    |    | 1  |    |    |    |    |    |   |   | 1 |   |   |   |   |   |   |   |  |

## Syntax

vqmul.q rd, rs, rt

## Description

Performs a vector-matrix homogeneous transform (matrix-vector product), with a vector result

## Instruction performance

Throughput: 4 cycles/instruction

Latency: 10 cycles

## Register overlap compatibility

Output register cannot overlap with input registers

## Allowed prefixes

- rt: Not supported

- rs: Not supported

- rd: Not supported